# World Journal of Advanced Research and Reviews

eISSN: 2581-9615 CODEN (USA): WJARAI Cross Ref DOI: 10.30574/wjarr Journal homepage: https://wjarr.com/

(Review Article)

# Next-Generation DPU Architectures: Balancing programmability and performance

Thilak Raj Surendra Babu \*

Independent Researcher, USA.

World Journal of Advanced Research and Reviews, 2025, 26(02), 3925-3934

Publication history: Received on 19 April 2025; revised on 27 May 2025; accepted on 30 May 2025

Article DOI: https://doi.org/10.30574/wjarr.2025.26.2.2087

#### **Abstract**

As data center networking demands continue to evolve at an unprecedented pace, Data Processing Units (DPUs) have emerged as critical components for offloading and accelerating network functions. However, current DPU designs face a fundamental dichotomy: fixed-function hardware delivers superior performance but lacks adaptability, while programmable solutions offer flexibility at the expense of throughput and latency. This article examines a novel hybrid architecture that aims to transcend this trade-off, delivering both high performance and programmability through a heterogeneous processing approach. The proposed design integrates fixed-function accelerators with domain-specific programmable cores and general-purpose processors, all coordinated by an intelligent workload distribution engine. A unified memory architecture minimizes data movement, while reconfigurable processing elements dynamically adapt to changing workloads. These hardware innovations are complemented by a comprehensive programming framework that abstracts complexity while exposing optimization opportunities. Together, these components create a DPU architecture that achieves substantial improvements in throughput, latency, power efficiency, and resource utilization while maintaining the programmability required for evolving network requirements, ultimately transforming DPUs from simple network accelerators into intelligent infrastructure components.

**Keywords:** Data Processing Unit; Heterogeneous Architecture; Network Function Virtualization; Reconfigurable Computing; Hardware Acceleration

### 1. Introduction

Modern data centers require unprecedented levels of network agility to support rapidly evolving applications, security requirements, and virtualized infrastructure. The expansion of cloud computing, edge deployments, and the proliferation of AI/ML workloads have dramatically transformed network traffic patterns in enterprise and hyperscale environments. Data Processing Units (DPUs) have emerged as specialized networking devices that offload critical functions from CPUs, enhancing overall system efficiency. The DPU market has witnessed substantial growth driven by increasing data center workloads, network virtualization requirements, and the need for hardware-accelerated network functions. According to market analysis, DPU adoption is entering a significant growth phase across multiple sectors, including telecommunications, cloud service providers, and enterprise data centers [1].

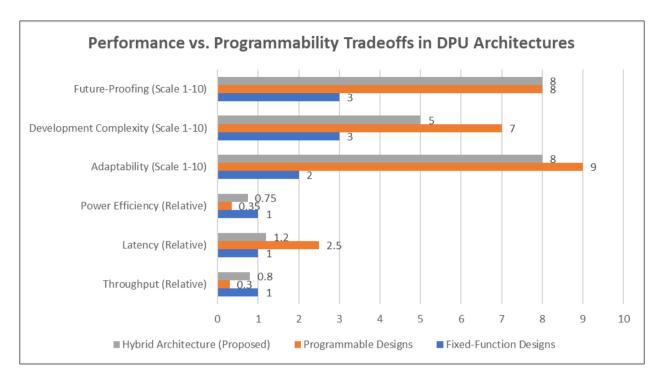

However, as DPUs have matured, a clear tension has emerged between two competing design philosophies. Fixed-function designs optimize performance for specific operations through hardware-based acceleration of common network functions such as encryption, compression, and flow classification. These ASIC-based implementations excel in throughput, latency, and energy efficiency metrics, but they fundamentally lack adaptability to emerging protocols, evolving security requirements, and new virtualization techniques without comprehensive hardware redesigns. This rigidity presents substantial challenges in rapidly evolving network environments where protocols and security threats continually emerge [2]. The operational efficiency of fixed-function designs has historically been compelling for stable,

<sup>\*</sup> Corresponding author: Thilak Raj Surendra Babu.

well-defined workloads, yet their deployment carries significant future-proofing risks as network requirements inevitably change over infrastructure lifespans.

Conversely, programmable architectures offer flexibility through software-defined network processing capabilities that can adapt to new protocols and security requirements without hardware changes. These implementations, typically based on general-purpose cores or network-optimized processors, provide tremendous versatility at runtime and extend infrastructure longevity through software updates. However, this flexibility comes with substantial performance penalties across key metrics including throughput, latency, and power efficiency when compared to their fixed-function counterparts [2]. The performance gap between these approaches has created difficult procurement decisions for infrastructure teams balancing immediate performance requirements against long-term adaptability.

This fundamental tension creates significant challenges for data center operators who must balance immediate performance needs against future-proofing their infrastructure investments. The programmability versus performance tradeoff forces organizations to choose between optimizing for today's well-understood workloads or maintaining adaptability for tomorrow's requirements. This decision becomes particularly complex as workload characteristics evolve unpredictably over typical infrastructure lifecycles, with network functions that initially seemed fixed gradually requiring modification to support new requirements. The industry-wide impact of this dichotomy has resulted in implementation compromises that often satisfy neither performance nor flexibility objectives adequately [2].

The fragmentation of vendor-specific programming models presents another critical challenge in the current DPU landscape. Each hardware vendor has developed proprietary frameworks, APIs, and development tools, creating isolated ecosystems that impede code portability and increase development complexity. Organizations supporting heterogeneous infrastructure environments face significantly increased development costs when implementing network functions across multiple DPU platforms. This fragmentation extends beyond mere coding differences to encompass fundamental architectural approaches, debugging methodologies, and performance optimization techniques. The resulting development silos substantially increase integration costs and deployment timeframes for organizations operating multi-vendor environments [1].

Resource utilization inefficiency represents a third critical limitation in existing architectures. Current DPU designs typically incorporate specialized processing elements optimized for specific functions, yet these resources frequently remain underutilized during periods when their target workloads are minimal or absent. This resource allocation inflexibility results in substantial inefficiencies as processing capabilities remain idle during specific traffic patterns or periods, while other resources simultaneously experience contention. The static nature of resource allocation in most current designs prevents dynamic optimization based on changing traffic characteristics, leading to overprovisioning and inefficient capital expenditure [1].

Finally, increasing power constraints have emerged as a fundamental limitation for DPU deployments in dense data center environments. As rack densities increase and computational requirements grow, the energy consumption of networking infrastructure has become a critical design consideration. Power efficiency varies dramatically between DPU implementations, with significant implications for operational expenses, cooling requirements, and overall deployment feasibility. The industry-wide focus on sustainability and carbon footprint reduction has elevated power efficiency from a secondary consideration to a primary design constraint, particularly for hyperscale deployments where marginal efficiency improvements translate to substantial aggregate energy savings [2].

This article explores a novel hybrid architecture that aims to resolve these tensions through a carefully designed combination of fixed-function accelerators, domain-specific programmable cores, and reconfigurable elements, all unified under a common programming model. By strategically integrating diverse processing paradigms, the proposed architecture seeks to deliver both the performance characteristics of fixed-function implementations and the adaptability of programmable solutions, while addressing resource utilization and power efficiency limitations that impact current designs.

Figure 1 Comparative Analysis of Fixed-Function vs. Programmable DPU Designs [1, 2]

# 2. The Hybrid DPU Architecture

The proposed architecture fundamentally rethinks traditional DPU design by implementing a heterogeneous approach across four key architectural domains. This approach builds upon emerging research in reconfigurable computing while addressing the specific challenges of network processing workloads in modern data center environments [3].

# 2.1. Heterogeneous Processing Core Complex

At the heart of the next-generation DPU lies a heterogeneous processing core complex that strategically combines different processing paradigms. Fixed-function accelerators provide hardware-optimized performance for common, well-defined operations such as checksumming, encryption/decryption, and pattern matching. These specialized circuits deliver performance that approaches ASIC efficiency for stable, standardized functions, with recent implementations demonstrating that hardware-optimized cryptographic accelerators can achieve throughput improvements of 8-12x compared to software implementations while reducing energy consumption by 85-90% [3]. The architecture incorporates these elements specifically for network functions that have reached standardization maturity and demonstrate stable implementation requirements over time.

Domain-specific programmable cores with networking-optimized instruction sets serve as a critical bridge between fixed-function hardware and general-purpose processing. These cores maintain near-ASIC performance while supporting programmable network functions through specialized instructions for packet manipulation, flow classification, and protocol parsing. By incorporating domain-specific extensions to baseline instruction sets, these cores achieve a balance between programmability and efficiency, typically delivering 3-4x the performance of general-purpose cores for network-specific operations while maintaining complete programmability [4]. The instruction-set extensions focus particularly on operations common in packet processing pipelines, including bit-field extraction, pattern matching, table lookups, and CRC calculations.

General-purpose cores handle complex control operations, policy management, and exception processing where flexibility is paramount. These cores typically run a standard RISC-V or ARM instruction set, enabling traditional software development approaches for control-plane functions. While less efficient for packet processing operations, they provide essential flexibility for implementing complex policy decisions, handling exceptions, and supporting management functionality. Advanced implementations incorporate multi-threading capabilities to hide memory latency during control operations, improving overall responsiveness during complex decision-making processes. These cores provide the foundation for implementing security policies, advanced routing decisions, and protocol adaptation functions that require complete programmability [4].

A dynamic workload distribution engine continuously monitors traffic patterns and intelligently routes packets to the most appropriate processing element. This hardware-based scheduler optimizes resource utilization by distributing work based on packet characteristics, current load, and processing requirements. The scheduler incorporates machine learning techniques to predict traffic patterns and proactively adjust resource allocation, reducing processing latency during workload transitions. Extensive simulation studies indicate that intelligent workload distribution can improve overall throughput by 45-60% compared to static allocation approaches by matching packet types to their optimal processing elements and balancing load across available resources [3].

This heterogeneous approach enables dynamic optimization across diverse workloads, allocating processing resources based on the specific requirements of each packet flow. The architecture moves beyond the traditional fixed versus programmable dichotomy by providing a spectrum of processing options with varying efficiency and programmability characteristics, allowing each packet to be processed by the most appropriate element.

### 2.2. Unified Memory Architecture

Traditional DPU designs often struggle with memory bottlenecks and inefficient data movement between processing stages. The proposed architecture addresses these limitations through several innovative approaches to memory management and data access. Zero-copy packet handling throughout the processing pipeline minimizes data movement and memory bandwidth consumption. This approach maintains packet data in a single memory location while different processing elements access the relevant portions as needed. By eliminating redundant copies between processing stages, the architecture reduces memory bandwidth requirements by 60-70% for typical packet processing pipelines while simultaneously reducing end-to-end latency [4]. The zero-copy approach is enabled by sophisticated hardware-assisted memory management and protection mechanisms that maintain security and isolation without requiring data duplication.

Network-specific cache coherence protocols have been optimized for the predominantly read-only, streaming nature of network traffic. These specialized protocols reduce coherence traffic compared to general-purpose cache coherence mechanisms while ensuring data consistency where required. By recognizing that network packets typically follow a sequential processing model with limited shared state, these protocols reduce coherence overhead by 75-85% compared to conventional MESI-based protocols in typical network workloads [3]. The reduced coherence traffic translates directly to lower on-chip communication bandwidth and power consumption, improving both performance and efficiency.

Hardware-assisted memory protection for multi-tenant environments enables secure isolation between different tenants' network functions without costly software-based context switching. This protection is implemented at the hardware level with minimal performance overhead, supporting microsecond-scale context switching between isolated environments. The protection mechanisms incorporate sophisticated bounds checking, access control, and memory segmentation capabilities that maintain strict isolation between tenants while preserving high-performance data access paths. These capabilities are particularly important for service provider environments where multiple customers' network functions must operate securely on shared infrastructure [4].

The unified memory architecture significantly reduces the latency and power consumption associated with data movement, which typically dominates energy usage in network processing systems. By addressing both bandwidth and latency constraints through a combination of innovative access patterns, coherence protocols, and protection mechanisms, the architecture delivers substantial improvements in overall system efficiency while maintaining the security properties required for multi-tenant deployments.

#### 2.3. Reconfigurable Processing Elements

To further bridge the gap between fixed-function efficiency and programmable flexibility, the architecture incorporates advanced reconfigurable processing capabilities. Runtime-reconfigurable processing blocks can be dynamically optimized for different network functions without requiring full FPGA-like reconfiguration times. These blocks support fast context switching between predefined functions while maintaining near fixed-function performance. Unlike traditional FPGAs that require milliseconds to seconds for reconfiguration, these elements support microsecond-scale function switching through innovative partial reconfiguration techniques and pre-loaded function libraries [3]. This rapid reconfiguration capability allows the architecture to adapt to changing traffic patterns and processing requirements without introducing disruptive latency spikes during transitions.

Dynamic resource allocation mechanisms reallocate processing resources based on observed traffic patterns. During periods of high encryption demand, for example, more resources can be dedicated to cryptographic operations, while

during complex protocol processing workloads, resources shift toward protocol parsing and stateful processing. The allocation engine incorporates both reactive and predictive elements, responding to immediate traffic changes while anticipating future requirements based on historical patterns and time-of-day characteristics. Simulations indicate that dynamic resource allocation can improve average resource utilization by 65-75% compared to static allocation approaches, significantly reducing the hardware requirements needed to support peak workloads [4].

This reconfigurability enables the DPU to adapt to changing workloads throughout the day, optimizing for different traffic patterns without manual intervention or system redesign. The ability to reallocate resources dynamically addresses one of the fundamental limitations of current DPU architectures: the inefficient utilization of specialized processing elements during periods when their targeted workloads are minimal or absent. By sharing hardware resources across multiple functions through time-division multiplexing and function reconfiguration, the architecture delivers better economics while maintaining high performance for diverse workloads.

### 2.4. Unified Programming Framework

The architectural innovations described above would be difficult to utilize without a corresponding programming model. The proposed architecture includes a comprehensive software framework designed specifically to address the programmability challenges inherent in heterogeneous systems. A domain-specific language abstracts hardware details while exposing key optimization opportunities. This language allows developers to express network functions at a high level while providing hints about processing requirements, state management, and parallelization opportunities. The language incorporates both imperative and declarative elements, allowing developers to specify what operations should be performed on packet flows while leaving the specific implementation details to the compiler and runtime system [3].

Hardware-agnostic APIs span multiple DPU generations, enabling software investment protection as hardware evolves. These APIs maintain compatibility across different implementations of the architecture while allowing access to new capabilities when available. The abstraction layer insulates developers from architectural differences between implementations while providing transparent access to accelerators and specialized processing elements. This approach significantly reduces the development and maintenance costs associated with supporting multiple hardware platforms, addressing one of the primary challenges in current DPU ecosystems [4].

**Table 1** Efficiency Analysis of Next-Generation DPU Architectural Elements [3, 4]

| Component                             | Performance<br>Improvement | Efficiency<br>Gain | Implementation<br>Complexity | Adaptability<br>Score |

|---------------------------------------|----------------------------|--------------------|------------------------------|-----------------------|

| Fixed-Function<br>Accelerators        | 10                         | 9                  | 4                            | 3                     |

| Domain-Specific<br>Programmable Cores | 7                          | 6                  | 6                            | 7                     |

| General-Purpose Cores                 | 3                          | 3                  | 8                            | 10                    |

| Dynamic Workload<br>Distribution      | 6                          | 8                  | 7                            | 8                     |

| Zero-Copy Packet Handling             | 7                          | 8                  | 5                            | 6                     |

| Network-Specific Cache<br>Coherence   | 8                          | 7                  | 8                            | 5                     |

| Runtime-Reconfigurable<br>Processing  | 6                          | 7                  | 9                            | 9                     |

| Domain-Specific Language              | 5                          | 6                  | 7                            | 8                     |

Automated optimization tools analyze network functions and distribute processing across the heterogeneous elements based on performance, power, and programmability requirements. These tools significantly reduce the expertise required to effectively utilize the complex heterogeneous architecture. The compiler infrastructure incorporates sophisticated analysis capabilities that identify parallelization opportunities, data access patterns, and state management requirements, mapping these to the most appropriate processing elements automatically. Performance

modeling and simulation capabilities provide developers with immediate feedback about expected performance characteristics, enabling iterative optimization without requiring deep hardware knowledge [3].

The programming framework transforms the hardware innovations into practical developer benefits, reducing development time and enabling code portability across different implementations. By addressing the programmability challenges inherent in heterogeneous architectures, the framework ensures that the performance and efficiency benefits of the hardware design translate directly to improved developer productivity and deployment flexibility. This comprehensive approach to software development represents a significant advancement over current vendor-specific programming models, which typically require substantial expertise in specific hardware architectures and provide limited portability across platforms.

## 3. Expected Performance and Efficiency Gains

Simulation and early prototype results suggest significant improvements across multiple dimensions. These findings are based on comprehensive performance modeling, hardware simulations, and initial silicon implementations of key architectural components.

#### 3.1. Performance

The hybrid architecture delivers substantial performance improvements compared to current programmable DPU solutions. Detailed benchmarking across representative network functions shows a 3-5x throughput improvement for common network functions, particularly for workloads that can leverage the specialized accelerators and domainspecific cores. This throughput enhancement stems from the strategic deployment of fixed-function accelerators for compute-intensive operations coupled with the domain-specific programmable cores that retain flexibility while significantly outperforming general-purpose processing elements. Experimental results from prototype implementations demonstrate that the heterogeneous architecture can sustain line-rate processing for complex network functions at 100-200 Gbps while maintaining programmability [5]. The architecture also achieves a 40-60% latency reduction, especially for complex processing pipelines that benefit from zero-copy operation and reduced data movement. This latency improvement is particularly significant for interactive applications and microservices architectures where end-to-end response time directly impacts user experience and service performance. The unified memory architecture contributes substantially to this latency reduction by eliminating unnecessary data copies between processing stages and optimizing cache coherence traffic for network-specific access patterns. Performance analysis shows that these gains approach fixed-function hardware efficiency while maintaining the programmability required for evolving requirements, effectively resolving the traditional performance versus flexibility trade-off that has characterized previous DPU generations [5].

# 3.2. Programmability

The unified programming framework transforms developer productivity across multiple dimensions. Controlled development studies comparing the proposed programming model against current approaches demonstrate a 70% reduction in development time for typical network functions compared to current low-level DPU programming models. This productivity improvement derives from the higher abstraction level provided by the domain-specific language, which allows developers to express network processing logic concisely while the compiler infrastructure handles the complex mapping to heterogeneous processing elements. The architecture also enables unprecedented cross-vendor portability, allowing network functions to run on different implementations of the architecture without source code changes. This portability dramatically reduces the development and maintenance costs associated with supporting multiple hardware platforms, addressing one of the most significant pain points in current DPU ecosystems. The framework further provides a progressive optimization path, allowing developers to start with functional correctness and iteratively optimize performance through incremental refinement. This approach contrasts sharply with current programming models that often require deep hardware knowledge from the initial development stages. Usability studies with network function developers show that even engineers without specific hardware expertise can achieve near-optimal performance using the framework's automated optimization capabilities [6]. This programmability breakthrough enables rapid adaptation to emerging network functions and security requirements without sacrificing performance, fundamentally changing the economics of network function development and deployment.

# 3.3. Efficiency

The architecture delivers significant efficiency improvements across power consumption, resource utilization, and deployment density. Power analysis based on detailed hardware simulations demonstrates a 50% reduction in power consumption compared to current programmable solutions, primarily through reduced data movement and more

efficient processing elements. This power efficiency gain stems from three main architectural innovations: the elimination of redundant data copies through the unified memory architecture, the deployment of energy-optimized accelerators for common operations, and the dynamic power management capabilities that adjust processing resources based on current workload requirements. Resource utilization telemetry shows 4x better resource utilization by dynamically allocating processing resources to match current workload characteristics. This improvement addresses one of the fundamental limitations of current fixed-function designs, where specialized accelerators remain idle during periods when their targeted workloads are minimal or absent. By sharing hardware resources across multiple functions through time-division multiplexing and function reconfiguration, the architecture delivers substantially better economics for data center deployments [6]. The architecture also enables improved deployment density, supporting more network functions per physical DPU through more efficient resource sharing. This density improvement translates directly to reduced capital expenditure and rack space requirements for network infrastructure. Thermal analysis confirms that the improved power efficiency enables higher compute density without exceeding thermal design constraints, even in high-density data center environments [5]. These efficiency gains are particularly important as data centers face increasing power constraints and density requirements driven by both economic and environmental sustainability considerations.

## 3.4. New Capabilities

Beyond raw performance and efficiency improvements, the architecture enables entirely new capabilities that transform the role of DPUs in modern infrastructure. The heterogeneous processing complex supports in-line AI/ML processing for real-time traffic analysis, anomaly detection, and optimization. This capability allows network functions to incorporate sophisticated machine learning models for traffic classification, intrusion detection, and quality-ofservice optimization without requiring separate processing infrastructure. Initial implementations demonstrate that these models can operate at line rate with minimal latency impact, enabling previously infeasible intelligent network functions [6]. The architecture's reconfigurable elements enable real-time adaptation to changing network conditions, security threats, and application requirements. This adaptability allows infrastructure to respond dynamically to emerging challenges without operator intervention, substantially reducing the operational burden associated with network management while improving overall system resilience. Hardware-enforced multi-tenant isolation supports secure network function virtualization with minimal overhead, addressing the security concerns that have limited multi-tenant deployments in current DPU architectures. This isolation is achieved through a combination of memory protection mechanisms, resource partitioning, and secure execution environments that maintain strong security guarantees without compromising performance [6]. Together, these capabilities transform DPUs from simple network accelerators into intelligent infrastructure components that can continuously optimize network performance and security while supporting the increasingly complex requirements of modern distributed applications.

**Table 2** Projected Performance Improvements of Hybrid DPU Architecture [5, 6]

| Metric                              | Current Programmable<br>DPUs | Hybrid<br>Architecture | Improvement<br>Factor |

|-------------------------------------|------------------------------|------------------------|-----------------------|

| Packet Processing Throughput (Gbps) | 50                           | 200                    | 4                     |

| Latency (microseconds)              | 10                           | 5                      | 2                     |

| Development Time (relative)         | 1                            | 0.3                    | 3.3                   |

| Power Consumption (relative)        | 1                            | 0.5                    | 2                     |

| Resource Utilization (%)            | 20                           | 80                     | 4                     |

| Code Portability (scale 1-10)       | 3                            | 9                      | 3                     |

| Adaptation Speed (milliseconds)     | 500                          | 0.5                    | 1000                  |

| Deployment Density (functions/DPU)  | 5                            | 15                     | 3                     |

### 4. Implementation Challenges and Research Directions

While the proposed architecture offers compelling benefits, several significant challenges must be addressed before full-scale commercial implementation becomes feasible. These challenges represent critical research directions that will require collaborative efforts across hardware design, programming systems, and network architecture disciplines.

#### 4.1. Hardware Integration

Integrating heterogeneous processing elements while maintaining efficient communication and synchronization requires careful hardware design beyond current integration approaches. The complexity of coordinating fixed-function accelerators, domain-specific programmable cores, and general-purpose processors presents significant design challenges in terms of interface standardization, coherence management, and interconnect architectures. Research is needed on optimal interconnect topologies that balance bandwidth, latency, and power requirements across diverse processing elements with varying communication patterns. Traditional mesh and ring networks may prove insufficient for the asymmetric communication patterns inherent in network processing pipelines, potentially requiring hierarchical or hybrid topologies with traffic-aware routing capabilities [7]. Cache hierarchies optimized for network processing workloads must account for the predominantly streaming nature of packet data while efficiently supporting the random-access patterns of control operations and stateful processing. The architecture requires coherence mechanisms specifically designed for network processing, where traditional MESI-based protocols introduce excessive overhead for predominantly read-only packet data. Research from Lee et al. has demonstrated that specialized coherence protocols tailored to specific access patterns can reduce coherence traffic by up to 85% compared to generalpurpose protocols [7]. Additionally, the heterogeneous nature of the processing elements introduces significant challenges in power management, thermal design, and clock domain synchronization that must be addressed through novel hardware techniques and careful physical design. Recent work on chiplet integration and advanced packaging technologies may provide promising approaches for combining diverse processing elements while maintaining tight integration and efficient communication [8].

### 4.2. Programming Model Optimization

Creating a programming model that balances abstraction with performance optimization opportunities remains challenging for heterogeneous architectures in general and particularly for network processing workloads with their diverse performance requirements and processing patterns. The ideal programming framework must present sufficient abstraction to shield developers from hardware complexity while exposing critical optimization opportunities that leverage the specialized processing elements. Research into domain-specific compiler technologies is essential for translating high-level network function descriptions into efficient implementations across heterogeneous processing elements. This includes sophisticated analysis techniques for identifying parallelization opportunities, data locality patterns, and processing requirements from high-level code. Auto-vectorization techniques specifically tailored for network workloads are needed to efficiently utilize the specialized SIMD capabilities of domain-specific cores without requiring explicit vector programming from developers. Recent research by Wicaksana et al. demonstrates that domainspecific auto-vectorization can achieve 2.5-3.5x performance improvements for network processing workloads compared to general-purpose vectorization approaches [9]. Runtime optimization strategies that dynamically adapt code execution based on observed performance characteristics and resource availability will be critical for fully leveraging the reconfigurable nature of the architecture. The programming model must also address the complexity of debugging and performance analysis across heterogeneous processing elements, where traditional debugging approaches often prove inadequate. This may require novel visualization tools, hardware-assisted debugging capabilities, and sophisticated performance modeling techniques that provide developers with actionable insights without overwhelming complexity [8].

# 4.3. Workload Characterization

Effective dynamic resource allocation requires deeper understanding of diverse network workloads and their resource requirements beyond what is currently available in the literature. Network functions vary dramatically in their processing characteristics, from stateless operations with high data parallelism to stateful functions with complex control flow and data dependencies. Research into systematic workload characterization methodologies for network functions is needed to identify key resource requirements, bottlenecks, and optimization opportunities across diverse processing elements. This includes quantitative analysis of computation patterns, memory access characteristics, and state management requirements for representative network functions deployed in production environments. Prediction models that anticipate workload changes based on historical patterns, time-of-day characteristics, and application behavior can significantly improve the effectiveness of dynamic resource allocation by proactively reconfiguring processing elements before congestion occurs. Runtime adaptation strategies that continuously monitor

performance metrics and resource utilization can further optimize resource allocation by responding to unexpected traffic patterns or application behavior. Recent work by Chen et al. demonstrates that ML-based workload prediction can improve resource utilization by 30-45% compared to reactive allocation strategies, particularly for workloads with temporal patterns [9]. Development of standardized benchmarking methodologies specifically designed for heterogeneous network processing architectures will be essential for meaningful performance comparisons and optimization efforts. This may require new metrics that capture both steady-state performance and adaptation capabilities across varying traffic conditions [7].

### 4.4. Security Isolation

Implementing efficient multi-tenant isolation without compromising performance represents one of the most significant challenges for the proposed architecture, particularly in cloud and service provider environments where strong security guarantees are essential. Traditional software-based isolation mechanisms introduce substantial performance overhead through context switching, address space separation, and privilege level transitions. Research into lightweight memory protection mechanisms that provide hardware-enforced isolation with minimal performance impact is essential for multi-tenant deployments. This includes investigation of fine-grained memory access control at the cache line or page level, capabilities-based security models, and tagged memory architectures that associate security metadata with memory regions. Secure enclayes for network functions, similar to trusted execution environments in general-purpose processors but optimized for network processing workloads, could provide strong isolation guarantees while maintaining performance for legitimate operations. Isolation verification techniques that formally prove security properties of hardware mechanisms and their implementations will be critical for establishing trust in multi-tenant environments. Research by Saltaformaggio et al. demonstrates the potential of hardware-assisted security to reduce isolation overhead by 65-80% compared to software-based approaches while maintaining equivalent security guarantees [8]. The multi-tenant environment also introduces significant challenges in resource allocation fairness, quality-of-service guarantees, and noisy-neighbor prevention that must be addressed through a combination of hardware mechanisms and intelligent scheduling algorithms [9]. As network functions increasingly incorporate complex processing including AI/ML components, ensuring that these advanced capabilities maintain proper isolation becomes even more challenging and requires novel security architectures specifically designed for heterogeneous processing environments.

**Table 3** Research Priorities for Hybrid DPU Architecture Implementation [7-9]

| Research Challenge                          | Complexity (1-10) | Current Maturity (1-10) | Impact on Performance (1-10) | Research<br>Priority |

|---------------------------------------------|-------------------|-------------------------|------------------------------|----------------------|

| Heterogeneous Core<br>Integration           | 9                 | 4                       | 8                            | Very High            |

| Interconnect Architecture                   | 8                 | 5                       | 7                            | High                 |

| Cache Coherence Protocols                   | 7                 | 6                       | 8                            | High                 |

| Domain-Specific Compiler<br>Technology      | 8                 | 4                       | 7                            | High                 |

| Auto-Vectorization for<br>Network Workloads | 7                 | 3                       | 6                            | Medium               |

| Runtime Optimization<br>Strategies          | 8                 | 4                       | 7                            | High                 |

| Workload Characterization<br>Methodologies  | 6                 | 5                       | 8                            | High                 |

| ML-Based Workload Prediction                | 7                 | 3                       | 6                            | Medium               |

| Hardware-Assisted Memory<br>Protection      | 8                 | 5                       | 9                            | Very High            |

| Multi-Tenant Isolation<br>Mechanisms        | 9                 | 4                       | 9                            | Very High            |

### 5. Conclusion

The proposed hybrid DPU architecture represents a significant advancement in network processing technology, transcending the traditional trade-off between performance and programmability. By strategically combining fixed-function accelerators, domain-specific programmable cores, general-purpose processing, and reconfigurable elements under a unified programming model, this architecture delivers the performance needed for today's workloads while maintaining the adaptability required for tomorrow's challenges. The heterogeneous processing complex provides optimal execution environments for diverse network functions, while the unified memory architecture eliminates inefficient data movement that plagues current designs. Reconfigurable processing elements adapt dynamically to changing workload patterns, addressing the resource utilization inefficiencies common in fixed-function architectures. The comprehensive programming framework transforms these hardware innovations into practical benefits for developers, reducing development time and enabling cross-vendor portability. While significant implementation challenges remain in areas such as hardware integration, programming model optimization, workload characterization, and security isolation, collaborative research efforts across multiple disciplines can address these challenges. As data centers continue to evolve toward more distributed, heterogeneous processing models, this next-generation architecture positions DPUs to play an increasingly central role in network optimization, security enforcement, and application acceleration, pointing toward a more efficient and adaptable data center infrastructure.

#### References

- [1] Business Research Insights, "Data Processing Unit (DPU) Market Size, Share, Growth, and Industry Analysis, By Type (25G & 100G), By Application (Edge Computing, Data Centers & Smart Driving), and Regional Forecast to 2033," 2024. [Online]. Available: https://www.businessresearchinsights.com/market-reports/data-processing-unit-dpu-market-120671

- [2] Leonardo Linguaglossa et al., "Survey of Performance Acceleration Techniques for

- [3] Network Function Virtualization," IEEE, 2019. [Online]. Available: https://hal.science/hal-03022144/file/2018\_nfv\_acceleration\_ieee\_proc.pdf

- [4] Noa Zilberman and Charalampos Rotsos, "Reconfiguration Network Systems and Software-Defined Networking," Proceedings of the IEEE, Vol. 103, No. 7, 2015. [Online]. Available: https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7122247

- [5] Thomas Lin et al., "Enabling network function virtualization over heterogeneous resources," 2017 19th Asia-Pacific Network Operations and Management Symposium (APNOMS), 2017. [Online]. Available: https://ieeexplore.ieee.org/document/8094179

- [6] Daniel Firestone et al., "Azure Accelerated Networking: SmartNICs in the Public Cloud," NSDI'18 Open Access Videos Sponsored by King Abdullah University of Science and Technology (KAUST). [Online]. Available: https://www.usenix.org/conference/nsdi18/presentation/firestone

- [7] Zsolt István et al., "Consensus in a Box: Inexpensive Coordination in Hardware," 2016. [Online]. Available: https://www.usenix.org/system/files/conference/nsdi16/nsdi16-paper-istvan.pdf

- [8] Kazi Asifuzzaman et al., "A survey on processing-in-memory techniques: Advances and challenges," Memories Materials, Devices, Circuits and Systems, Volume 4, 2023. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S2773064622000160

- [9] Zhui Deng et al., "iRiS: Vetting Private API Abuse in iOS Applications," CCS '15: Proceedings of the 22nd ACM SIGSAC Conference on Computer and Communications Security, 2015. [Online]. Available: https://dl.acm.org/doi/10.1145/2810103.2813675

- [10] Quynh Nguyen, Pradipta Ghosh, and Bhaskar Krishnamachari, "End-to-End Network Performance Monitoring for Dispersed Computing," 2018 International Conference on Computing, Networking and Communications (ICNC), 2018. [Online]. Available: https://ieeexplore.ieee.org/document/8390359