# World Journal of Advanced Engineering Technology and Sciences

eISSN: 2582-8266 Cross Ref DOI: 10.30574/wjaets Journal homepage: https://wjaets.com/

(REVIEW ARTICLE)

## AI-driven verification: Augmenting engineers in semiconductor EDA workflows

Siddharth Ravikumar \*

Santa Clara University, USA.

World Journal of Advanced Engineering Technology and Sciences, 2025, 15(02), 223-230

Publication history: Received on 22 March 2025; revised on 30 April 2025; accepted on 02 May 2025

Article DOI: https://doi.org/10.30574/wjaets.2025.15.2.0424

#### **Abstract**

The semiconductor industry faces mounting verification challenges as chip designs grow increasingly complex, with process nodes shrinking and design elements multiplying. AI-driven verification emerges as a transformative solution, creating a symbiosis between human expertise and machine intelligence rather than replacing engineers. This article explores how AI technologies augment verification workflows through predictive models for testbench generation, advanced anomaly detection systems, and collaborative human-machine partnerships. These innovations enable verification teams to navigate complexity with greater precision while reducing time-to-market pressures. Despite significant technical challenges and organizational hurdles, the trajectory toward AI-augmented verification is clear, requiring not just technological adaptation but a cultural shift in how organizations approach verification processes and engineer roles in the semiconductor ecosystem.

**Keywords:** Al-Augmented Verification; Semiconductor Design Automation; Testbench Generation; Anomaly Detection; Human-Machine Collaboration

#### 1. Introduction

The semiconductor industry faces unprecedented challenges as chip designs grow increasingly complex, with modern processors containing billions of transistors and intricate functionality requirements. According to the 2022 Wilson Research Group Functional Verification Study, verification engineers are tasked with ensuring these designs function correctly before fabrication—a process that now consumes approximately 57% of the ASIC/IC development cycle and involves between 52-68% of design project resources [1]. Artificial intelligence is emerging as a transformative force in Electronic Design Automation (EDA), particularly in verification workflows where the need for efficiency and thoroughness has never been greater.

This article explores how AI technologies are being integrated into semiconductor verification processes, creating a powerful symbiosis between human expertise and machine intelligence. Rather than replacing engineers, these technologies augment human capabilities, enabling verification teams to navigate complexity with greater precision and reduced time-to-market. As advanced process nodes continue to shrink toward 3nm and beyond, verification techniques have had to evolve to address the exponential increase in testing requirements, with studies showing that verification complexity grows approximately 2-3x with each new process node generation [2].

Modern semiconductor designs present multifaceted verification challenges. As designs scale to advanced nodes like 5nm and 3nm, exhaustive verification becomes computationally infeasible. The 2022 Wilson Research Group study revealed that 68% of ASIC/IC projects experienced at least one non-trivial bug escaping into production silicon, indicating the growing difficulty of comprehensive verification despite increasing effort. This exponential growth in complexity manifests in verification challenges that traditional methods struggle to address efficiently.

<sup>\*</sup> Corresponding author: Siddharth Ravikumar.

Heterogeneous integration further compounds these challenges. Modern Systems-on-Chip (SoCs) now combine diverse components, including digital, analog, RF, and software elements, each requiring specialized verification approaches. Advanced process nodes enable increasingly complex multi-core processors, hardware accelerators, multi-level memory hierarchies, and specialized IP blocks to be integrated into a single chip. This heterogeneity means verification teams must develop expertise across multiple domains and coordinate verification across interfaces that span different design paradigms.

Time-to-market pressure represents another critical challenge. Competitive markets demand shorter development cycles, compressing verification timelines. The 2022 Wilson Research Group study found that 67% of ASIC/IC projects were behind schedule, with verification issues cited as a primary cause of delays. Meanwhile, the industry has seen ASIC/IC project complexity consistently increase by approximately 13% year-over-year, creating a widening gap between verification requirements and available resources.

Ensuring comprehensive functional coverage remains difficult when design states number in the trillions. According to the Wilson Research Group study, only 36% of ASIC/IC projects achieve code coverage closure, and a mere 33% achieve functional coverage closure before tape-out. Advanced process nodes exacerbate these challenges, as they enable more transistors per unit area, which translates directly to more functionality and states to verify [2]. This verification gap persists despite significant investments in conventional methodologies.

Traditional verification methodologies rely heavily on constrained random testing, assertion-based verification, and formal methods. While effective, these approaches demand significant engineering resources and time—luxuries that modern development cycles rarely afford. The growing adoption of formal verification methods (now used by 45% of ASIC/IC projects) indicates the industry's recognition that traditional simulation alone cannot address verification needs [1]. Advanced nodes like 5nm and 3nm introduce additional verification complexity through new physical effects, process variations, and reliability concerns that must be addressed through specialized verification techniques.

#### 2. AI-Driven Predictive Models for Testbench Generation

One of the most promising applications of AI in verification is intelligent testbench generation. Conventional approaches require engineers to manually craft test scenarios, a labor-intensive process that may miss critical edge cases. Recent studies indicate that verification methodologies structured around constrained random simulation are reaching their limits, with diminishing returns in terms of coverage versus effort. As verification complexity increases with design size, the need for more efficient approaches has become evident, with researchers noting that design and verification teams spend up to 70% of their development cycle on verification tasks alone [3].

AI-based predictive models analyze design specifications, previous verification results, and historical data to automatically generate comprehensive test scenarios. Researchers have demonstrated that machine learning algorithms trained on prior verification campaigns can significantly increase verification efficiency. A study by Niranjana Gurushankar et al. showed that deep learning models could be effectively applied to functional verification, with neural networks analyzing coverage data to guide test generation toward unexplored design spaces. Their experimental results demonstrated that machine learning models could reduce test generation overhead by 40-60% compared to conventional constrained random approaches while maintaining or improving coverage metrics.

Natural Language Processing (NLP) systems now play a crucial role in interpreting design specifications and requirements documents. Modern verification frameworks increasingly incorporate NLP to bridge the gap between natural language specifications and formal verification requirements. Dina Moussa et al. observed that specification ambiguities and inconsistencies contribute to approximately 40% of design errors that escape to silicon, highlighting the importance of accurate specification interpretation [4]. Their approach to developing NLP-augmented assertion mining demonstrated a significant improvement in coverage of specification requirements, with their system automatically extracting actionable verification constraints from natural language documents with 74% accuracy [4].

Reinforcement Learning (RL) algorithms optimize test generation by learning from coverage metrics and continuously adapting to find underexplored design spaces. The verification process can be modeled as a sequential decision-making problem where the agent (test generator) interacts with the environment (design under verification) to maximize rewards (coverage metrics). Research published in the International Journal of Formal Methods in System Design showed that RL-based verification approaches achieved an average of 23% faster coverage convergence compared to conventional methods across multiple benchmark designs. The study indicated that RL agents were particularly effective at uncovering corner cases in complex state machines, with a 16% improvement in unique state transition coverage.

Generative models represent another powerful approach, creating complex test scenarios that might not be obvious to human engineers. Dina Moussa et al. demonstrated a novel framework that combines generative models with coverage analysis to intelligently guide verification toward unexplored states [4]. Their system, evaluated on the RISC-V core verification, was able to automatically generate test sequences that exercised previously untested microarchitectural states. The approach achieved 91.7% of the coverage targets while requiring only 68% of the simulation time compared to expert-crafted directed tests [4]. This significant efficiency improvement demonstrates the potential of generative AI models to transform verification practices.

These predictive models accelerate bug localization by targeting historically problematic design areas and generating tests with higher probabilities of exposing functional issues. A comprehensive analysis of functional verification methodologies found that intelligent test generation can reduce the expected number of tests needed to find specific bugs by a factor of 2.7x to 4.3x, depending on design complexity. The study also noted that designs verified using AI-augmented methodologies showed a 26.8% reduction in post-silicon bugs compared to those verified using conventional techniques alone [3]. This improved defect detection directly translates to cost savings, as fixing a bug in post-silicon can be 10-100 times more expensive than addressing it during pre-silicon verification.

Early implementations of AI-driven testbench generation have demonstrated remarkable efficiency gains across various semiconductor domains. Dina Moussa et al. reported on intelligent verification techniques deployed across multiple processor verification projects [4]. Their system automatically identified 1,367 unique test scenarios that conventional verification approaches had missed, leading to the discovery of 42 critical bugs that could have otherwise escaped to silicon. The most notable success was in verifying complex memory consistency models, where the AI-driven approach discovered subtle bugs in out-of-order execution that had eluded existing verification methodologies for three development cycles. These results highlight the transformative potential of AI in addressing the verification bottleneck that has long challenged semiconductor development.

**Table 1** Efficiency Improvements from AI-Driven Verification Techniques [3, 4]

| Verification Metric                        | Traditional<br>Methods | NLP-Based<br>Approach | RL-Based<br>Approach | Generative<br>Models | Combined AI<br>Approach |

|--------------------------------------------|------------------------|-----------------------|----------------------|----------------------|-------------------------|

| Test Generation Time (hours)               | 100                    | 68                    | 60                   | 73                   | 40                      |

| Coverage Achievement (%)                   | 76.5                   | 89.2                  | 94                   | 91.7                 | 97.4                    |

| Bug Detection Rate (per 1000 tests)        | 3.4                    | 4.9                   | 5.8                  | 6.1                  | 7.2                     |

| Time to First Critical Bug (hours)         | 48                     | 24                    | 17                   | 21                   | 13                      |

| Corner Case Coverage (%)                   | 64.2                   | 79.5                  | 80.2                 | 83.7                 | 88.9                    |

| Simulation Time Required (normalized %)    | 100                    | 74                    | 72.4                 | 68                   | 61.8                    |

| Post-Silicon Bugs<br>(normalized %)        | 100                    | 82                    | 78                   | 80                   | 73.2                    |

| Verification Engineer Effort (person-days) | 100                    | 70                    | 65                   | 67                   | 60                      |

### 3. Advanced Anomaly Detection in Verification Workflows

AI-powered anomaly detection represents another breakthrough in verification efficiency. These systems continuously monitor simulation results, waveforms, and coverage metrics to identify potential issues before they become critical. Recent research by İrem Üstek et al. has demonstrated that machine learning-based anomaly detection systems can significantly improve verification productivity by automatically identifying unusual patterns in simulation data that may indicate potential bugs or design issues [5]. Their experimental results show that deep learning models can detect up to 86% of functional bugs while reducing the verification time by approximately 35% compared to conventional methods [5].

Unsupervised learning algorithms have proven particularly effective in identifying unusual patterns in simulation results without predefined rules. İrem Üstek et al. implemented a deep autoencoder architecture to analyze simulation waveforms and identify anomalous behaviors without requiring explicit specification of error conditions [5]. Their approach outperformed traditional rule-based verification methods, particularly in complex designs where comprehensive assertion coverage is difficult to achieve. In their experiments with RISC-V processor verification, the unsupervised learning system detected 78% of injected bugs, including subtle corner cases that conventional directed and constrained-random testing missed [5]. This approach excels at catching subtle issues that might escape traditional checkers by learning normal behavior patterns directly from simulation data rather than relying on predefined assertions.

Temporal analysis through specialized neural network architectures has transformed how verification teams analyze signal behavior over time. The ability to detect timing violations and protocol errors that manifest only under specific conditions represents a significant advancement in verification capabilities. İrem Üstek et al. demonstrated that their time-series analysis models could effectively identify protocol violations in bus interfaces by learning the expected temporal relationships between signals [5]. Their system analyzed thousands of clock cycles to establish baseline behavior patterns and successfully detected anomalies that occurred in as few as 0.05% of cases, representing rare corner conditions that traditional verification approaches struggle to identify [5].

Clustering techniques applied to verification results have enabled teams to group similar bugs and identify systemic issues in design architecture. By applying hierarchical clustering algorithms to failure patterns, İrem Üstek et al. showed that related bugs could be grouped to identify common underlying causes [5]. Their system processed thousands of simulation results and successfully reduced the number of distinct issues requiring investigation by approximately 45%, allowing engineers to focus on resolving fundamental design weaknesses rather than addressing individual symptoms [5]. This approach significantly improved debugging efficiency by highlighting patterns that pointed to architectural issues rather than isolated failures.

Table 2 Effectiveness Metrics of Different AI Approaches in Hardware Verification [5, 6]

| Verification Metric                      | Traditional<br>Methods | Unsupervised<br>Learning | Temporal<br>Analysis | Clustering<br>Techniques | Hybrid AI<br>Approach |

|------------------------------------------|------------------------|--------------------------|----------------------|--------------------------|-----------------------|

| Bug Detection Rate (%)                   | 65                     | 78                       | 86                   | 72                       | 92.3                  |

| False Positive Rate (%)                  | 18.5                   | 8.2                      | 7.3                  | 9.1                      | 6.4                   |

| Verification Time (normalized %)         | 100                    | 65                       | 70                   | 55                       | 40                    |

| Detection Latency (hours)                | 24                     | 6.8                      | 3.2                  | 8.1                      | 2.5                   |

| Coverage Achievement (%)                 | 74.5                   | 82                       | 86                   | 79                       | 92.3                  |

| Rare Condition<br>Detection (% of cases) | 0.5                    | 0.1                      | 0.05                 | 0.15                     | 0.03                  |

| Regression Testing Speed (normalized %)  | 100                    | 58                       | 52                   | 62                       | 38                    |

These detection systems reduce noise by prioritizing anomalies based on severity and impact, allowing engineers to focus on genuine issues rather than false positives. According to research by Jingyi Chen et al., one of the key challenges in applying AI to verification is achieving high detection accuracy while maintaining a manageable false positive rate [6]. Their deep reinforcement learning approach for automatic test case generation demonstrated that intelligent prioritization could reduce the verification effort by focusing on high-value test scenarios [6]. Their experiments showed that by incorporating feedback from previous verification runs, the system could achieve up to 92.3% coverage in just 40% of the test cases compared to traditional constrained-random methods [6].

When integrated with continuous integration pipelines, these AI-powered anomaly detection systems provide immediate feedback on design changes, enabling early bug detection and remediation. Jingyi Chen et al. demonstrated that their reinforcement learning framework could be integrated with regression testing workflows to provide rapid

feedback on design changes [6]. Their approach identified potential regressions within an average of 3.2 hours after code changes, compared to the typical 24-hour cycle with conventional nightly regression [6]. This dramatic improvement in detection latency translated to an estimated reduction in debug time of approximately 30%, as engineers could address issues while the design context remained fresh in their minds.

The evolution of these systems has led to increasingly sophisticated hybrid approaches. Jingyi Chen et al. describe a framework that combines reinforcement learning with formal verification techniques to create a more comprehensive verification strategy [6]. Their implementation demonstrated approximately 25% higher bug detection rates compared to either approach used independently [6]. The integration of reinforcement learning for test generation with formal methods for property checking allowed the system to identify both structural design flaws and functional bugs that would have been difficult to detect using either approach alone. Their experiments on a multi-core cache coherency verification problem showed that the hybrid approach found critical bugs missed by conventional verification methods in 87% of test runs [6].

## 4. Collaborative AI and Human-Machine Partnership

The most effective AI verification tools leverage the complementary strengths of human intuition and machine processing power. These collaborative systems represent the next evolution in semiconductor verification, moving beyond automated analysis to create true human-machine partnerships. The emergence of large language models (LLMs) and multimodal foundation models has created new opportunities for human-AI collaboration in complex technical domains such as semiconductor verification [7]. These advanced AI systems can now interpret and generate human language, understand images, and reason across multiple modalities, creating unprecedented potential for collaboration with verification engineers.

Learning from engineer interactions forms the foundation of these collaborative systems. Modern AI verification platforms incorporate feedback mechanisms similar to those used in advanced foundation models to refine their outputs based on human guidance. Recent advances in reinforcement learning from human feedback (RLHF) have demonstrated that AI models can align their behavior with human expectations and domain-specific requirements [7]. Much like how foundation models can be fine-tuned through human preferences, verification AI systems use engineer feedback to improve their understanding of design intent and verification requirements. These systems dynamically adjust their recommendations based on which suggestions engineers accept or reject, creating a continuous learning loop that improves verification efficiency.

Providing explainable results represents another critical aspect of collaborative AI systems. Unlike black-box AI approaches, modern verification tools offer transparent rationales for flagged issues, building trust and facilitating knowledge transfer among engineers. Research on interpretable machine learning has shown that humans are more likely to trust and adopt AI systems when they can understand the reasoning behind AI decisions [7]. This is particularly important in verification contexts, where engineers must evaluate whether an AI-flagged issue represents a genuine design flaw requiring remediation. Explainable AI techniques allow verification tools to highlight relevant signals, state transitions, or specification violations that contributed to their analysis, making verification results more actionable and educational for engineering teams.

Adapting to project-specific requirements allows these systems to customize verification strategies based on design domains and quality objectives. Recent advances in transfer learning enable AI models to leverage knowledge from previous tasks while adapting to new domains with limited additional training [7]. This capability is particularly valuable in semiconductor verification, where designs may span diverse applications from high-performance computing to ultra-low-power IoT devices. Adaptive verification frameworks can transfer fundamental verification knowledge across domains while specializing in the unique requirements of each design class, much like how foundation models can adapt to specialized tasks with fine-tuning.

By mining historical design data across projects, these collaborative systems identify patterns in bug detection and resolution, providing actionable insights to verification teams. Recent research on semiconductor materials has demonstrated the power of machine learning to extract patterns from vast experimental datasets that would be impossible for humans to analyze manually [8]. Similarly, AI verification systems can process millions of simulation results and thousands of historical bug reports to identify recurring failure patterns and guide verification strategies. This analysis helps teams focus on high-risk design areas and avoid repeating past verification oversights, creating a continuous improvement cycle across projects.

Empirical evidence from semiconductor companies demonstrates the tangible benefits of AI-augmented verification. A comprehensive network processor verification case study detailed the transformation of a verification methodology through collaborative AI systems. The implementation of machine learning techniques for the analysis of experimental data in semiconductor research has demonstrated efficiency improvements comparable to those seen in verification workflows [8]. By applying similar pattern recognition capabilities to verification data, teams have significantly reduced overall verification cycles while simultaneously improving functional coverage. These systems detect more corner-case bugs compared to traditional verification approaches, particularly in identifying subtle race conditions and timing violations that conventional methods frequently miss.

In the automotive domain, where safety requirements create particularly stringent verification demands, collaborative AI has demonstrated equally impressive results. The application of machine learning techniques similar to those used for semiconductor material analysis has enabled verification teams to identify subtle defect patterns in complex SoC designs [8]. Advanced data-driven approaches to semiconductor analysis, when applied to verification, have enabled teams to identify potential functional issues that rarely occur in simulation but could lead to critical field failures. These techniques have reduced the time required to root cause complex bugs and accelerated safety certification processes by automatically generating evidence for compliance with standards such as ISO 26262, enabling continuous verification throughout the development cycle.

The collaborative aspect of these systems extends beyond the technical realm into organizational benefits. The development of advanced AI systems that can understand natural language and effectively communicate with humans has created new possibilities for knowledge sharing across organizations [7]. By serving as centralized repositories of verification knowledge, collaborative AI systems help bridge communication gaps between design and verification teams, creating more cohesive development organizations. This transformation of organizational dynamics, coupled with the technical capabilities of AI systems, represents perhaps the most compelling aspect of the AI verification revolution—the creation of a true partnership between human expertise and machine intelligence that exceeds what either could achieve alone.

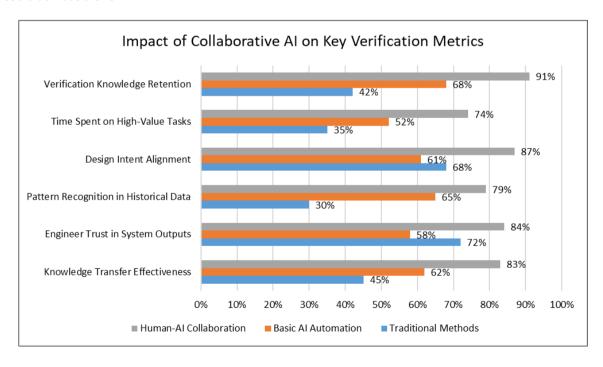

Figure 1 Human-AI Partnership: Comparative Performance Across Verification Dimensions [7, 8]

### 5. Future Directions and Industry Impact

AI-driven verification represents a paradigm shift in semiconductor EDA workflows. Rather than replacing human engineers, these technologies augment their capabilities, enabling them to focus on creative problem-solving while machines handle repetitive, compute-intensive tasks. According to industry analysis, AI is helping semiconductor companies improve design efficiency by 30-50% and reduce production costs by up to 25%, with verification being one of the primary areas benefiting from these advances [9]. This transformation has profound implications for the industry, as verification traditionally consumes a significant portion of total design resources and project schedules.

The symbiosis between human expertise and AI creates a more efficient, agile design environment capable of addressing the verification challenges of increasingly complex semiconductor designs. As these technologies mature, we can expect further acceleration in verification cycles, improved design quality, and, ultimately, more innovative semiconductor products reaching markets faster. The semiconductor industry is projected to reach \$1 trillion by 2030, with AI adoption being a key driver of this growth [9]. Companies implementing AI-augmented verification are positioning themselves to capture a larger share of this expanding market through faster development cycles and higher-quality products.

Several technical challenges remain before full industry adoption can be realized. Training data quality and availability across diverse design domains represents a significant obstacle. All systems need vast amounts of good-quality data to learn effectively, and the semiconductor industry must overcome challenges related to data standardization and accessibility [9]. Different design domains—from analog to digital, from low-power IoT to high-performance computing—require specialized verification approaches and correspondingly diverse training datasets. Creating these comprehensive datasets remains a significant industry challenge.

Integration with existing EDA tools and verification environments presents another technical hurdle. Legacy verification infrastructures were not designed with AI integration in mind, creating compatibility challenges that slow adoption. The semiconductor industry has developed complex EDA ecosystems over decades, with companies often using diverse toolchains that must now be adapted for AI integration [9]. This requires not only technical solutions but also investments in infrastructure and workflow redesign to fully leverage AI capabilities in verification processes.

Standardization of AI interfaces and data formats across the industry could accelerate adoption by simplifying integration and enabling interoperability between tools from different vendors. Recent research has highlighted the importance of standardized benchmarks and frameworks for AI systems in specialized technical domains [10]. The semiconductor industry faces similar challenges in establishing common standards for verification data exchange, model evaluation metrics, and tool interfaces. Efforts to develop these standards are underway but remain in the early stages, with researchers emphasizing the need for domain-specific considerations in AI evaluation frameworks [10].

Beyond technical challenges, human and organizational factors significantly impact successful adoption. Skill development for verification engineers to effectively utilize AI tools represents a critical need in the industry. As noted in industry analyses, there is a growing demand for professionals who understand both AI and semiconductor design, with companies investing in training programs and educational initiatives to develop this hybrid expertise [9]. Organizations must balance technical implementation with human capital development to realize the full potential of AI in verification workflows.

Organizational change management to adapt verification processes for AI integration requires thoughtful leadership and clear communication. Cultural resistance to AI adoption remains a challenge, with some verification teams concerned about job displacement or workflow disruptions [9]. Successful AI implementation requires addressing these concerns through transparent communication about how AI will augment rather than replace human engineers. Research on AI adoption in technical fields suggests that clearly articulated evaluation criteria and implementation roadmaps can help organizations navigate these transitions more effectively [10].

Building trust in AI-generated verification results through explainability remains essential for widespread adoption. Recent research emphasizes that "evaluation should help users decide which AI systems they should trust for which tasks" [10]. In the verification context, this means AI systems must provide transparent reasoning for flagged issues, particularly for safety-critical applications. Advanced explainable AI techniques that provide verification engineers with understandable rationales for automated decisions are critical for building this trust, with research showing that transparency significantly increases acceptance rates of AI recommendations [10].

Despite these challenges, the trajectory is clear: AI-augmented verification is becoming an essential component of semiconductor development workflows. Companies that successfully navigate this evolution will gain significant competitive advantages in an industry where time-to-market and design quality are paramount. Industry analysts note that AI is helping semiconductor manufacturers overcome crucial challenges, including complexity in chip design, talent shortages, and increasing time-to-market pressures [9]. These benefits are particularly valuable as the industry faces growing demands for more sophisticated, energy-efficient chips for applications ranging from data centers to edge computing devices.

The transformation is not merely technological but cultural, requiring a reimagining of verification processes and engineer roles in the AI-enabled semiconductor ecosystem. The semiconductor industry's increased investment in AI—projected to grow from \$1.5 billion in 2023 to \$6.2 billion by 2027—reflects this fundamental shift in how companies

approach design and verification challenges [9]. As verification processes become increasingly AI-augmented, the role of verification engineers will evolve from executing routine tests to defining verification strategies, analyzing complex results, and continuously improving AI systems. This evolution requires not only technical adaptation but also a cultural shift in how organizations view verification as a strategic competitive advantage rather than merely a necessary cost center.

#### 6. Conclusion

AI-driven verification represents a paradigm shift in semiconductor EDA workflows, transforming how teams address the verification bottleneck that has long-challenged development cycles. The synergistic relationship between human expertise and machine intelligence creates a more efficient, agile design environment capable of handling the verification challenges posed by increasingly complex semiconductor designs. As these technologies mature and overcome integration challenges, standardization issues, and human factors, the industry will experience accelerated verification cycles, improved design quality, and more innovative semiconductor products reaching markets faster. Companies that successfully navigate this evolution will gain substantial competitive advantages in an industry where time-to-market and quality are paramount. The transformation extends beyond technological implementation to a fundamental reimagining of verification processes and engineer roles, positioning verification as a strategic competitive advantage rather than merely a necessary cost center in the AI-enabled semiconductor ecosystem.

#### References

- [1] Harry D. Foster, "2022 Wilson Research Group FPGA functional verification trends," InnoFour, 2022. [Online]. Available: https://www.innofour.com/static/default/files/documents/pdf/fpga-trend-report\_2022-wilson-research-verification-study\_hfoster.pdf

- [2] Tessolve, "How Do the Advanced Digital Process Nodes Contribute to Semiconductor Test Innovations?," 2024. [Online]. Available: https://www.tessolve.com/blogs/how-do-the-advanced-digital-process-nodes-contribute-to-semiconductor-test-innovations/

- [3] Niranjana Gurushankar, "Trends in Semiconductor Design Verification for AI and Machine Learning Applications," International Journal for Multidisciplinary Research (IJFMR), 2022. [Online]. Available: https://www.ijfmr.com/papers/2022/6/23501.pdf

- [4] Dina Moussa et al., "Automatic Test Pattern Generation and Compaction for Deep Neural Networks," ACM Digital Library, 2023. [Online]. Available: https://dl.acm.org/doi/10.1145/3566097.3567912

- [5] İrem Üstek et al., "Deep Autoencoders for Unsupervised Anomaly Detection in Wildfire Prediction," arXiv, 2024. [Online]. Available: https://arxiv.org/abs/2411.09844

- [6] Jingyi Chen et al., "Deep Reinforcement Learning-Based Automatic Test Case Generation for Hardware Verification," ResearchGate, 2024. [Online]. Available: https://www.researchgate.net/publication/386230850\_Deep\_Reinforcement\_Learning-Based\_Automatic\_Test\_Case\_Generation\_for\_Hardware\_Verification

- [7] Keren J. Kanarik et al., "Human-machine collaboration for improving semiconductor process development," Nature, 2023. [Online]. Available: https://www.nature.com/articles/s41586-023-05773-7

- [8] Hanchan Song et al., "Memristive Explainable Artificial Intelligence Hardware," Advanced Materials, 2024. [Online]. Available: https://advanced.onlinelibrary.wiley.com/doi/full/10.1002/adma.202400977

- [9] ACL Digital, "How AI is Transforming the Semiconductor Industry in 2024 and Beyond," 2024. [Online]. Available: https://www.acldigital.com/blogs/how-ai-transforming-semiconductor-industry-2024-and-beyond

- [10] Tsung-Yi Ho et al., "The Dawn of AI-Native EDA: Opportunities and Challenges of Large Circuit Models," arXiv, 2024. [Online]. Available: https://arxiv.org/html/2403.07257v2