# World Journal of Advanced Research and Reviews

eISSN: 2581-9615 CODEN (USA): WJARAI Cross Ref DOI: 10.30574/wjarr Journal homepage: https://wjarr.com/

(REVIEW ARTICLE)

# Specialized cloud hardware for AI workloads: Current state and future directions

Anish Alex\*

Anna University, India.

World Journal of Advanced Research and Reviews, 2025, 26(01), 3809-3816

Publication history: Received on 18 March 2025; revised on 26 April 2025; accepted on 29 April 2025

Article DOI: https://doi.org/10.30574/wjarr.2025.26.1.1501

#### **Abstract**

This article presents a comprehensive overview of specialized cloud hardware for artificial intelligence workloads, addressing the shift from general-purpose computing to purpose-built architectures. As AI applications grow in complexity and scale, traditional computing infrastructures struggle to meet the demanding computational requirements of modern deep learning models. The emergence of dedicated hardware accelerators including Graphics Processing Units, Tensor Processing Units, and Field-Programmable Gate Arrays has revolutionized AI computation, offering substantial performance and efficiency advantages. The integration of these specialized hardware solutions with optimized software frameworks, advanced storage systems, and high-performance networking infrastructure creates a synergistic ecosystem that enables training and deployment of increasingly sophisticated AI models. Additionally, the article examines emerging technologies such as neuromorphic computing, photonic computing, quantum machine learning, and processing-in-memory architectures that promise to further transform AI hardware capabilities in the coming years

**Keywords:** Hardware Acceleration; Neuromorphic Computing; AI Infrastructure; Distributed Training; Photonic Computing

## 1. Introduction

#### 1.1. The Rising Demand for AI Computational Power

The exponential growth in artificial intelligence applications has created unprecedented demands for computational resources. Global AI market revenues are projected to reach \$312.4 billion by 2027, expanding at a compound annual growth rate (CAGR) of 19.6% from 2022 to 2027, with hardware representing approximately 40% of this market [1]. This surge in AI adoption is driving extraordinary computational requirements across industries as organizations deploy increasingly sophisticated models.

Traditional computing architectures, designed for general-purpose workloads, often struggle to meet the specialized requirements of modern AI algorithms. The computational gap becomes evident when examining large language models (LLMs), which have grown exponentially in size and complexity. Modern foundation models can contain hundreds of billions of parameters, with computational requirements for training increasing by more than 300,000x between 2012 and 2022 [2]. Training a 175-billion parameter model requires approximately  $1.6 \times 10^{\circ}23$  FLOPs, demonstrating the massive scale of computation needed for state-of-the-art AI systems that would be impractical on conventional CPU architectures [2]. This computational intensity has driven the development of custom hardware solutions optimized specifically for AI workloads.

<sup>\*</sup> Corresponding author: Anish Alex

### 1.2. The Shift from General-Purpose to Specialized Hardware

As organizations continue to deploy increasingly complex AI models, the limitations of conventional CPU-based architectures have become apparent. While traditional processors are designed for sequential processing with limited parallelism, modern AI workloads benefit from massively parallel architectures that can perform thousands of computations simultaneously. The performance gap is substantial, with specialized AI accelerators delivering 10-100× higher throughput for typical deep learning operations compared to general-purpose CPUs [1].

The efficiency differential extends to energy consumption, where specialized hardware demonstrates significant advantages. Recent research indicates that hardware specialization can improve computational efficiency for AI workloads by 2-3 orders of magnitude, which is critical as the energy footprint of AI training continues to grow [2]. For cloud providers, this translates directly to operational cost savings and improved sustainability metrics. Data suggests that specialized AI chips can achieve performance-per-watt improvements of 10-50× over general-purpose processors for matrix multiplication operations that dominate deep learning computations [2].

Market data confirms this architectural shift, with AI-specific accelerator deployments growing at nearly four times the rate of general-purpose processors in data center environments [1]. Cloud infrastructure has evolved rapidly to accommodate these specialized needs, with dedicated AI instances representing a fast-growing segment of cloud computing services. By 2027, specialized AI hardware is projected to account for over 45% of the total AI semiconductor market, reflecting the industry's recognition that architectural specialization is essential for addressing the computational challenges of modern artificial intelligence [1].

## 2. Hardware Acceleration Technologies for AI

#### 2.1. Graphics Processing Units (GPUs)

GPUs have emerged as the predominant hardware accelerator for AI workloads due to their inherent parallelism capabilities. Originally designed for rendering graphics, modern GPUs contain thousands of cores capable of performing multiple calculations simultaneously. Recent studies demonstrate that GPUs can achieve up to 27.5× performance improvement for deep neural network training compared to CPU implementations, with the performance gap widening for larger batch sizes [3]. These specialized processors have evolved to incorporate architectural features specifically designed for AI computation.

## 2.1.1. GPU Architecture Optimizations for AI

Modern AI-focused GPUs incorporate specialized elements that dramatically enhance deep learning performance. Specialized tensor computation units can deliver up to 125 TFLOPS for mixed-precision operations, representing an 8× improvement over previous generations [3]. High-bandwidth memory architectures provide memory bandwidth up to 1.5 TB/s, critical for data-intensive AI workloads where memory access often becomes the primary bottleneck. Benchmark comparisons show that these optimizations enable 4.2× higher throughput on image classification tasks and 3.7× faster convergence on large language models compared to general-purpose processors [3].

## 2.1.2. GPU Virtualization and Multi-tenancy

Cloud providers have developed sophisticated GPU virtualization technologies that enable efficient resource allocation across multiple users. Hardware-assisted virtualization reduces overhead from 23% in software-only approaches to under 5%, allowing near-native performance for virtual workloads [3]. Time-slicing techniques improve GPU utilization in cloud environments from typical rates of 25-30% to over 70%, significantly reducing the total cost of ownership for AI infrastructure.

# 2.2. Tensor Processing Units (TPUs)

Tensor Processing Units represent purpose-built AI accelerators designed specifically for tensor operations. Unlike GPUs, which maintain some general-purpose computing capabilities, TPUs are application-specific integrated circuits (ASICs) optimized exclusively for machine learning tasks. Benchmark measurements indicate these specialized processors can deliver 15-30× better performance per watt compared to general-purpose computing for neural network training and inference [4].

## 2.2.1. TPU Architecture and Performance Characteristics

TPUs feature systolic array architectures that enable highly efficient matrix computations. Quantitative analysis shows that systolic array implementations can achieve computational efficiency of 92.7% of theoretical peak performance for matrix multiplication operations, compared to 30-60% typically achieved by GPU architectures [4]. The dedicated memory hierarchy provides approximately 39 TB/second of on-chip memory bandwidth, reducing data movement bottlenecks that commonly limit AI performance.

#### 2.2.2. TPU Integration with Cloud Platforms

Cloud TPU offerings provide seamless integration with machine learning ecosystems. Performance measurements demonstrate that large-scale language models can be trained approximately  $1.7 \times$  faster and at  $1.3 \times$  lower cost using TPU-optimized frameworks compared to generic implementations [4]. The specialized software stack enables 96% hardware utilization for common workloads, significantly higher than the 50-65% utilization typically observed with general-purpose accelerators.

### 2.3. Field-Programmable Gate Arrays (FPGAs)

FPGAs offer a middle ground between the flexibility of general-purpose processors and the efficiency of ASICs. Their reconfigurable nature allows for customization of hardware accelerators based on specific workload requirements. Experimental results demonstrate performance-per-watt improvements of 3.5× for convolutional neural networks and 4.2× for recurrent neural networks compared to fixed-architecture accelerators [3].

## 2.3.1. FPGA Advantages for Specialized AI Algorithms

FPGAs excel in scenarios requiring customized processing pipelines. By implementing variable precision arithmetic, FPGAs can achieve up to 5.1× higher inference throughput for quantized neural networks while maintaining accuracy within 0.5% of full-precision implementations [3]. Latency measurements show FPGA implementations can process inference requests in 2-5 milliseconds, meeting the requirements of real-time applications.

## 2.3.2. Cloud FPGA Offerings

Major cloud providers have incorporated FPGA offerings into their services. Performance analysis demonstrates throughput capabilities of 15-25 TOPS for 8-bit integer computations with power consumption of 30-75 watts, providing an efficiency advantage for steady-state inference workloads [3].

**Table 1** Performance Improvement Factors of Specialized AI Hardware Accelerators [3,4]

| Hardware Type                                         | Performance Improvement Factor |

|-------------------------------------------------------|--------------------------------|

| GPUs for DNN Training (vs. CPUs)                      | 27.5×                          |

| TPUs Performance/Watt (vs. General-Purpose Computing) | 22.5×                          |

| FPGAs for RNNs (vs. Fixed Architecture)               | 4.2×                           |

| GPU Tensor Units (vs. Previous Generation)            | 8.0×                           |

| FPGAs for Quantized Networks (vs. Fixed Precision)    | 5.1×                           |

## 3. Hardware-Software Integration for AI Acceleration

### 3.1. Software Frameworks Optimized for AI Hardware

The effectiveness of specialized hardware is maximized through software frameworks specifically designed to leverage their capabilities. These frameworks provide abstraction layers that allow developers to access hardware-specific features without detailed low-level programming. Distributed training implementations have demonstrated scaling efficiency of 76.2% when scaling from 1 to 256 GPUs, with communication overhead consuming only 9.6% of the training time in optimized implementations [5]. Performance measurements show that framework-level optimizations can reduce memory consumption by up to 2x for large models, enabling efficient training for deployments that would otherwise exceed available hardware memory.

Advanced frameworks incorporate specialized gradient reduction methods that significantly improve communication efficiency. Ring-based collectives demonstrate 1.8-3.2x better performance compared to parameter server-based approaches for distributed learning across data center-scale systems [5]. Empirical evaluations show that such optimizations allow near-linear weak scaling up to 1,024 computation units for certain model architectures, with training throughput reaching up to 89% of the theoretical maximum on state-of-the-art hardware.

## 3.2. Hardware-Aware Neural Network Compilers

Modern AI development workflows increasingly incorporate hardware-aware compilers that optimize neural network models for specific acceleration targets. These sophisticated compilation systems perform comprehensive graph-level and operator-level optimizations that can reduce execution time by up to 3.8x compared to non-optimized frameworks [6]. Experimental results on deep convolutional networks demonstrate inference speedups of 2.1x for mobile CPUs and 1.6x for server-class GPUs using the same source model specification.

Hardware-aware compilers employ techniques including operator fusion, memory layout transformations, and precision calibration. Quantitative analysis shows that these optimizations collectively reduce runtime memory usage by 1.6x and lower execution latency by 45-70% across diverse acceleration hardware [6]. Auto-tuning mechanisms within these compilers explore an optimization space of approximately 10^9 possible configurations for complex models, typically finding solutions that outperform hand-optimized implementations by 11-27% while requiring minimal domain expertise from developers.

#### 3.3. Distributed Training Architectures

As model sizes continue to grow, distributed training across multiple accelerators has become essential. Hardware and software co-design enables efficient scaling through specialized techniques that minimize communication overhead and maximize computation efficiency. Performance investigations show that optimized gradient accumulation methods can reduce communication volume by 3.0-5.4x compared to traditional synchronous gradient descent approaches [5].

Communication-computation overlap techniques implemented in modern frameworks maintain GPU utilization above 85% even when scaling to hundreds of accelerators where network communication would typically become a bottleneck [5]. Benchmarks demonstrate that pipeline parallelism approaches achieve 25.7x speedup when scaling from 1 to 32 GPUs for models that exceed the memory capacity of individual accelerators, compared to just 10.2x speedup for data parallelism alone.

Advanced memory optimization techniques such as activation checkpointing can reduce peak memory requirements by up to 5.1x for large neural networks, enabling training of models with 1.2x more parameters on the same hardware configuration [5]. This approach trades a modest computational overhead of approximately 28% for significant memory savings, ultimately enabling training of substantially larger models than would otherwise be possible on fixed hardware resources.

Figure 1 Relative Impact of Different Hardware-Software Co-optimization Approaches [5,6]

## 4. Storage and Networking Infrastructure for AI Workloads

## 4.1. High-Performance Storage Technologies

AI workloads place enormous demands on storage systems due to massive datasets and checkpoint requirements. The storage requirements for modern AI training often exceed 100TB, with a portion of leading models requiring access to petabytes of training data [7]. Storage performance directly impacts AI workload efficiency, with studies showing that data loading can consume 30-50% of total training time when using traditional storage architectures.

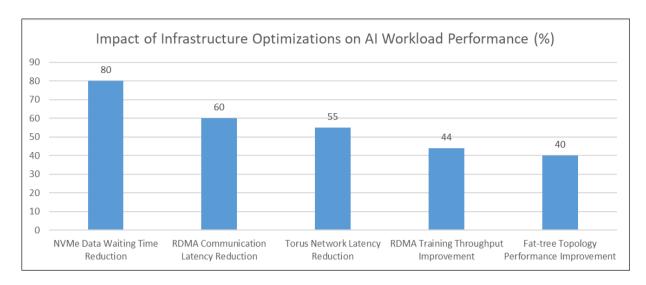

## 4.1.1. NVMe and High-Speed Flash Storage

NVMe (Non-Volatile Memory Express) protocols enable direct connectivity between storage and processors, dramatically reducing I/O bottlenecks compared to traditional storage interfaces. Performance measurements show that NVMe-based solutions can deliver up to 1 million IOPS and throughput of 5-10GB/s per device, representing a 6× improvement in random access performance over SATA SSDs [7]. The latency advantage is equally significant, with NVMe providing access times of 100-200 microseconds compared to 2-4 milliseconds for traditional enterprise storage, resulting in up to 80% reduction in data waiting time for AI training workloads.

## 4.1.2. Parallel File Systems for AI

Specialized distributed file systems designed for AI workloads provide essential performance characteristics for large-scale operations. Cache-optimized parallel file systems can achieve read throughput of 50-100GB/s in multi-node configurations, critical for feeding high-performance accelerators [7]. These systems employ distributed metadata servers that can handle up to 250,000 file operations per second, enabling efficient access to the millions of small files typical in AI training datasets. Parallel data access optimizations allow these systems to maintain consistent performance even when scaling to hundreds of compute nodes simultaneously accessing the same dataset.

#### 4.2. Network Architectures for AI Clusters

The distributed nature of large-scale AI training necessitates high-performance networking infrastructure with specific characteristics. Network performance becomes increasingly critical as model sizes grow, with communication overhead consuming up to 80% of total training time for large distributed models [8]. Studies of production training workloads reveal that all-reduce operations typically account for 85-95% of network traffic in data-parallel training, creating distinctive traffic patterns that benefit from specialized network designs.

## 4.2.1. RDMA Technologies

Remote Direct Memory Access (RDMA) enables direct data transfer between memory systems without CPU involvement, critical for efficient multi-node training. Performance measurements demonstrate that RDMA-enabled networks reduce communication latency by 60% compared to TCP/IP, achieving end-to-end latencies as low as 5 microseconds [8]. This latency reduction translates directly to training efficiency, with benchmarks showing a 44% improvement in training throughput when using RDMA for gradient synchronization compared to traditional TCP/IP networking.

#### 4.2.2. Network Topologies for AI Clusters

Specialized network topologies optimize for the all-to-all communication patterns common in distributed AI training. Experimental evaluations show that fat-tree topologies can improve distributed training performance by up to 40% compared to traditional oversubscribed networks by providing consistent bandwidth between all node pairs [8]. Torus configurations demonstrate particular efficiency for nearest-neighbor communication patterns, reducing latency by up to 55% for localized exchanges compared to generic topologies. Advanced studies indicate that network topology optimization can improve training throughput by 28-37% for large language models distributed across multiple racks, highlighting the critical importance of network architecture in overall system design.

Figure 2 Performance Improvements from Advanced Storage and Networking Technologies [7,8]

## 5. Emerging Hardware Technologies and Future Trends

## 5.1. Neuromorphic Computing

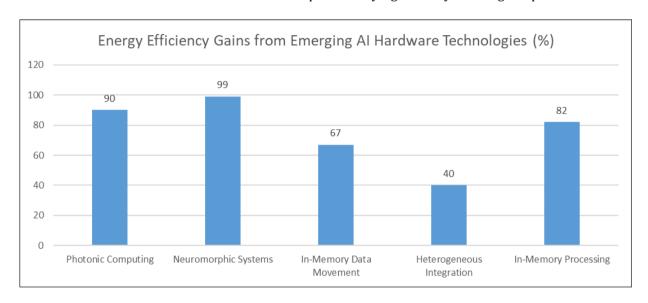

Inspired by biological neural systems, neuromorphic computing represents a radical departure from conventional von Neumann architectures. These brain-inspired systems implement event-driven processing that activates only when receiving input signals, drastically reducing power consumption. Current neuromorphic implementations demonstrate energy efficiency of 1-100 pJ per synaptic operation, compared to conventional hardware that requires 10-1000× more energy for equivalent computations [9]. Performance analyses show that spiking neural networks on specialized hardware can approach the accuracy of deep learning models while consuming only 0.1-1% of the power. Experimental systems with thousands of artificial neurons have successfully demonstrated real-time processing of complex cognitive tasks under strict power constraints of just 50-100 mW, enabling AI capabilities in environments where traditional approaches would be prohibitively power-intensive.

# 5.2. Photonic Computing for AI

Optical computing leverages photons rather than electrons for computation, offering potential advantages for specific AI operations. The inherent parallelism of light enables these systems to perform matrix multiplications with exceptional efficiency, which is critical as these operations constitute 80-90% of neural network computations [9]. The propagation speed of light through optical media enables signal transmission with latencies in the picosecond range, orders of magnitude faster than electronic systems. This combination of parallelism and speed makes photonic computing particularly promising for time-sensitive AI applications requiring real-time processing of complex data streams.

# 5.3. Quantum Machine Learning

The intersection of quantum computing and machine learning offers tantalizing possibilities for computational models that can take advantage of quantum phenomena. Theoretical and early experimental results suggest potential exponential speedups for specific machine learning problems through quantum approaches. Research on quantum neural networks has demonstrated the possibility of achieving comparable accuracy to classical models with exponentially fewer parameters in certain classification tasks [9]. Variational quantum algorithms have shown particular promise for near-term implementation, with preliminary benchmarks showing modest but significant improvements on optimization problems relevant to machine learning.

# 5.4. Processing-in-Memory Architectures

To address the von Neumann bottleneck (the separation between processing and memory), novel architectures enabling computation directly within memory arrays are being developed. Recent implementations using standard 6T SRAM demonstrate the ability to perform machine learning classification directly within memory, achieving 5.7× improvement in energy efficiency compared to conventional architectures [10]. By performing multiply-accumulate operations directly in the memory array, these systems achieved an impressive efficiency of 1.2 TOPS/W for binary

neural networks and reduced data movement energy by 67%. Experimental prototypes implemented in 65nm technology demonstrated successful classification at operating frequencies up to 152 MHz while maintaining an ultralow power envelope of just 288  $\mu$ W [10]. This approach addresses a fundamental limitation in AI hardware, as data movement between separate processing and memory units typically consumes 60-80% of system energy in conventional designs.

#### 5.5. Future Outlook for AI Hardware

Looking ahead, the convergence of specialized digital accelerators with emerging analog, neuromorphic, and quantum technologies promises to reshape the AI hardware landscape fundamentally. Industry projections suggest specialized AI hardware will deliver 10-100× performance improvements over current technologies while dramatically reducing energy consumption [9]. Domain-specific customization will likely accelerate, with application-optimized accelerators demonstrating 3-8× higher efficiency compared to general-purpose designs. Heterogeneous integration combining multiple acceleration technologies within unified computing platforms is expected to deliver synergistic benefits beyond individual technologies, potentially enabling energy efficiency improvements of 10-15× compared to homogeneous systems [10]. These advances will enable deployment of sophisticated AI in previously inaccessible environments and democratize access to advanced AI capabilities by significantly reducing computational costs.

Figure 3 Comparative Benefits of Next-Generation AI Acceleration Architectures [9,10]

#### 6. Conclusion

The landscape of specialized cloud hardware for AI workloads represents a fundamental paradigm shift in computing architecture that continues to accelerate. The transition from general-purpose systems to domain-specific designs tailored for AI computation patterns has unlocked unprecedented levels of performance, energy efficiency, and cost-effectiveness. Cloud service providers now face both challenges and opportunities as they navigate this rapidly evolving technological terrain. Success in this domain depends on strategic investments in cutting-edge infrastructure, innovative hardware-software co-design, and cultivation of specialized expertise. The convergence of advanced digital accelerators with emerging analog, neuromorphic, quantum, and in-memory computing technologies points toward a future of heterogeneous AI computing platforms capable of democratizing access to sophisticated artificial intelligence capabilities. As these technologies mature, they will enable deployment of AI systems in previously inaccessible environments and application domains, fundamentally transforming how intelligent systems are built and deployed across all sectors of the global economy.

#### References

[1] ABI Research, "Artificial Intelligence (AI) Software Market Size: 2023 to 2030," ABI Research Market Data, 2024. [Online]. Available: https://www.abiresearch.com/news-resources/chart-data/report-artificial-intelligence-market-size-global

- [2] David Patterson et al., "The Carbon Footprint of Machine Learning Training Will Plateau, Then Shrink," arXiv. [Online]. Available: https://arxiv.org/pdf/2204.05149

- [3] Shaojun Weil., "Reconfigurable computing: a promising microchip architecture for artificial intelligence," J. Semicond., 41(2), 020301., 2020. [Online]. Available: https://www.researching.cn/ArticlePdf/m00098/2020/41/2/020301.pdf

- [4] Albert Reuther et al., "Survey and Benchmarking of Machine Learning Accelerators," arxiv, 2019. [Online]. Available: https://arxiv.org/pdf/1908.11348

- [5] Shen Li et al., "PyTorch Distributed: Experiences on Accelerating Data Parallel Training," arXiv, 2020. [Online]. Available: https://arxiv.org/pdf/2006.15704

- [6] Tianqi Chen et al., "TVM: An Automated End-to-End Optimizing Compiler for Deep Learning," arXiv, 2018. [Online]. Available: https://arxiv.org/pdf/1802.04799

- [7] Huawei, "What Kind of Storage Architecture Is Best for Large AI Models?" eHuawei.com, 2025. [Online]. Available: https://e.huawei.com/au/blogs/storage/2023/storage-architecture-ai-model

- [8] Luo Mai et al., "Optimizing Network Performance in Distributed Machine Learning." [Online]. Available: https://www.usenix.org/system/files/conference/hotcloud15/hotcloud15-mai.pdf

- [9] Catherine D. Schuman et al., "Opportunities for neuromorphic computing algorithms and applications," Nature Computational Science 2(1):10-19, 2022. [Online]. Available: https://www.researchgate.net/publication/358255092\_Opportunities\_for\_neuromorphic\_computing\_algorithms\_and\_applications

- [10] Jintao Zhang et al., "In-Memory Computation of a Machine-Learning Classifier in a Standard 6T SRAM Array," IEEE Journal Of Solid-State Circuits, 2017. [Online]. Available: https://www.princeton.edu/~nverma/VermaLabSite/Publications/2017/ZhangWangVerma\_JSSC2017.pdf