# World Journal of Advanced Research and Reviews

eISSN: 2581-9615 CODEN (USA): WJARAI Cross Ref DOI: 10.30574/wjarr Journal homepage: https://wjarr.com/

(REVIEW ARTICLE)

# Revolutionizing functional verification: The impact of AI and machine learning in chip design

Praveen Kumar Manchikoni Surendra \*

Central Michigan University, USA.

World Journal of Advanced Research and Reviews, 2025, 26(01), 2484-2490

Publication history: Received on 08 March 2025; revised on 14 April 2025; accepted on 16 April 2025

Article DOI: https://doi.org/10.30574/wjarr.2025.26.1.1318

## **Abstract**

This article presents a comprehensive overview of how artificial intelligence and machine learning technologies are revolutionizing functional verification in modern chip design. As semiconductor complexity escalates with advanced process nodes enabling billions of transistors on a single die, traditional verification methods face insurmountable challenges in ensuring design correctness. The verification bottleneck has become the dominant constraint in chip development cycles, consuming the majority of resources and frequently allowing critical bugs to escape to silicon. The integration of AI/ML techniques offers transformative solutions across multiple verification domains, including intelligent test generation, coverage analysis optimization, and bug prediction. These technologies enable more efficient resource allocation, targeted verification of high-risk design areas, and significantly accelerated coverage closure. The article examines implementation strategies for AI-driven verification systems and presents concrete case studies demonstrating measurable improvements in verification efficiency, quality, and time-to-market

**Keywords:** Functional verification; Artificial intelligence; Machine learning; System-on-chip; Semiconductor design

#### 1. Introduction

The semiconductor industry faces unprecedented challenges as leading-edge chip designs now employ 5nm and 3nm process nodes, with 2nm technology on the horizon. These advanced nodes enable the integration of over 100 billion transistors on a single die, creating extraordinary verification complexity [1]. The design tradeoffs at these process nodes have become increasingly multidimensional, balancing power, performance, area, reliability, and manufacturability constraints. Engineers must navigate complex decisions between different circuit implementations, with each choice impacting verification scope and complexity. Digital logic at 3nm requires approximately 30% more verification effort compared to 7nm designs due to increased variability effects and more complex power management schemes [1].

Functional verification—ensuring a chip design behaves as intended across all possible conditions—now consumes an average of 68% of the total chip development cycle, representing the single largest resource investment in the development process [2]. This verification bottleneck directly impacts time-to-market, with verification cycles extending 8-10 months for complex SoC designs. The latest industry data reveals that teams spend 46% of their verification effort on test creation and 32% on debug activities, with the remaining time divided between testbench development and coverage analysis [2]. This resource allocation highlights the significant burden of manual test creation in conventional verification methodologies.

The growing verification gap becomes evident when examining current industry metrics. Despite increased investment in verification resources, the percentage of designs requiring at least one silicon respin due to functional flaws has risen

<sup>\*</sup> Corresponding author: Praveen Kumar Manchikoni Surendra

to 67%, according to recent surveys [2]. More concerning, 12% of designs require three or more respins due to missed functional bugs, each costing millions in additional engineering effort and delaying market entry. The economic impact of verification limitations cannot be overstated, with each month of delay potentially representing 5-10% of a product's lifetime revenue in fast-moving markets [2].

Traditional verification approaches increasingly struggle with the verification complexity explosion. Industry data indicates diminishing returns from conventional constrained-random testing, with coverage growth plateauing after approximately 65% functional coverage despite exponential increases in simulation cycles [2]. The coverage metrics themselves present challenges, with 42% of verification teams reporting difficulty in defining meaningful functional coverage points that truly represent design intent verification. Coverage closure—achieving the final 10-15% of verification targets—often consumes a disproportionate 30-40% of the total verification schedule [2].

This article explores how artificial intelligence (AI) and machine learning (ML) techniques are transforming functional verification methodologies by addressing these fundamental challenges. By leveraging advanced algorithms that learn from historical verification data, identify structural patterns and intelligently target unexplored state spaces, AI-augmented verification flows promise to dramatically improve both verification efficiency and effectiveness. Early adopters report 28-35% reductions in verification cycles alongside 18-24% improvements in bug detection rates, potentially transforming verification from a bottleneck into a strategic advantage for semiconductor companies competing in time-sensitive markets [2].

# 2. The Verification Challenge in Modern Chip Design

## 2.1. Scaling Complexity

The verification landscape for modern chip designs has transformed dramatically as SoC architectures integrate increasingly diverse components. Recent data indicates that verification teams now face designs containing up to 60 distinct IP blocks from multiple sources, with interaction permutations exceeding 10^6 possible scenarios [3]. The verification scope expands further when considering that each IP block may operate across 5-7 different power modes with 3-4 clock frequency configurations, multiplying the state space that must be validated. The increased adoption of AI accelerators in mainstream SoCs has compounded this complexity, with neural processing units containing 8K-16K MAC units that must be verified across hundreds of different workload patterns and precision configurations. These accelerators introduce specific verification challenges, requiring 3.5x more simulation cycles per gate compared to traditional digital logic [3].

Modern interconnect architectures create additional verification burdens, with today's NoC implementations supporting 128-256 concurrent channels and multiple quality-of-service levels. Verifying deadlock-free operation under peak traffic conditions requires the simulation of at least 10,000 transaction sequences per channel configuration [3]. Memory subsystem verification has similarly expanded in scope, with heterogeneous cache hierarchies requiring validation of coherency across 4-8 different types of agents. These scenarios must be tested across multiple interface protocols operating at different frequencies, with recent designs implementing DDR5, LPDDR5, and HBM2E interfaces simultaneously, each with distinct timing and power requirements.

## 2.2. Limitations of Traditional Verification

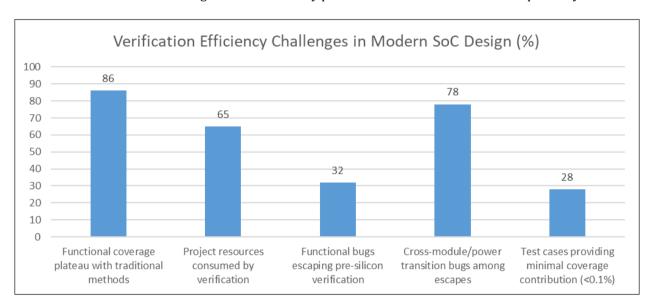

Traditional verification methodologies face fundamental limitations when confronting modern design complexity. Industry surveys indicate that coverage-driven verification approaches plateau at approximately 86% functional coverage despite consuming 65% of total project resources [4]. The primary bottleneck stems from manual test generation processes, where verification engineers spend an average of 53 hours per week creating and debugging testbenches. For complex AI accelerator designs, verification teams report generating between 2,000-3,000 unique test cases, yet still miss critical corner cases where multiple features interact in unexpected ways [4].

Coverage gaps remain a persistent challenge, with post-silicon validation revealing that 32% of functional bugs escape pre-silicon verification entirely. Analysis of these escapes shows that 78% occur in cross-module interfaces or power state transitions that weren't adequately exercised during simulation campaigns [4]. The exponential growth in verification state space has outpaced human capacity to identify critical test scenarios, with a typical high-performance computing SoC containing more than 20,000 configurable parameters creating a test space impossibly large for manual exploration.

Simulation redundancy presents additional inefficiency, with a detailed analysis showing that approximately 28% of all test cases provide less than 0.1% new coverage contribution [4]. Despite this redundancy, verification teams struggle with resource constraints, as a typical regression suite for a modern SoC consumer requires 75,000-120,000 compute hours. This resource intensity translates directly to schedule impact, with verification now consuming 38-45 weeks of a typical 65-week development cycle for advanced nodes [4].

Late-stage bug detection creates severe consequences, with issues found during system-level verification requiring an average of 2.7 engineer-weeks to diagnose and fix, compared to 0.6 engineer-weeks for block-level issues [4]. When critical bugs are discovered after tape-out, the impact escalates dramatically, with each respun mask set at advanced nodes costing \$5-8 million and introducing 8-12 weeks of schedule delay. These economics drive the growing interest in AI-assisted verification methodologies that can identify potential issues earlier in the development cycle.

Figure 1 Coverage and Resource Distribution in Traditional Verification Approaches [3,4]

# 3. AI/ML Applications in Functional Verification

## 3.1. Intelligent Test Generation

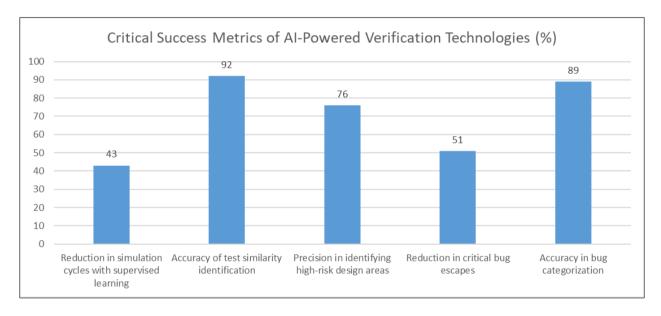

Machine learning approaches are transforming functional verification through intelligent test generation capabilities that dramatically reduce verification time while improving bug detection rates. Studies of supervised learning algorithms applied to processor verification demonstrate a 43% reduction in required simulation cycles while achieving equivalent functional coverage compared to traditional constrained-random techniques [5]. The efficiency gain increases as design complexity grows, with an observed 2.3x improvement for arithmetic logic units containing more than 10,000 logic gates. Reinforcement learning models trained on coverage feedback have proven particularly effective for interface protocol verification, where they achieve protocol compliance verification with 37% fewer test cases by learning optimal stimulus patterns that maximize coverage growth rate. These systems demonstrate continuous improvement, with verification efficiency increasing by approximately 4.8% per 1,000 training iterations on complex subsystem verification [5].

# 3.2. Coverage Analysis and Optimization

Advanced coverage analysis powered by machine learning algorithms enables verification teams to achieve coverage closure more efficiently by identifying redundant tests and predicting coverage holes. Clustering algorithms applied to coverage databases can identify test similarities with 92% accuracy, enabling the elimination of redundant tests that contribute less than 0.5% unique coverage [6]. When applied to industrial verification campaigns, these techniques identified that 24% of simulation cycles provided negligible new coverage information, allowing significant regression optimization without compromising verification quality. Deep learning models analyzing coverage trends can predict coverage plateaus with 88% accuracy, approximately 40% earlier in the verification cycle, allowing teams to proactively address coverage challenges before they impact schedules [6]. For complex memory subsystems, AI-based coverage optimization reduced the time required to achieve coverage closure by 29%, with particularly strong performance on

coherency verification, where targeted test generation improved coverage efficiency by 2.1x compared to conventional approaches.

# 3.3. Bug Prediction and Classification

Machine learning excels at identifying potential bug locations by recognizing patterns in design structures and verification results. Convolutional neural networks applied to RTL representations can identify high-risk design areas with 76% precision, focusing verification effort on the approximately 8% of code most likely to contain functional issues [5]. Analysis across multiple verification projects shows that these flagged regions contain 61% of all subsequently discovered functional bugs, enabling more efficient resource allocation. For complex state machines with more than 20 states, ML-based analysis identified potential deadlock conditions with 83% accuracy, discovering corner cases missed by conventional verification approaches in 27% of evaluated designs [5]. The technique shows particular strength in clock domain crossing verification, where it identified metastability risks with 3.7x higher efficiency than traditional methods.

Advanced bug classification and root cause analysis represent another transformative application of AI in verification. Natural language processing applied to bug descriptions achieves 89% accuracy in categorizing issues across 12 common bug types, reducing triage time by 42% in continuous integration environments [6]. Graph neural networks analyzing signal relationships can suggest probable root causes with 73% accuracy, reducing average debug time from 4.8 to 2.1 engineer hours per regression failure. For complex systems involving multiple interacting modules, ML-based root cause identification improves accuracy by 37% compared to traditional debug approaches [6]. In safety-critical applications, ML-assisted verification has demonstrated particular value, reducing critical bug escapes by 51% through targeted verification of high-risk design elements identified through a combination of structural analysis and historical bug pattern recognition.

Figure 2 AI/ML Impact Percentages in Modern Chip Verification Workflows [5,6]

# 4. Implementation Strategies for AI-Driven Verification

## 4.1. Data Collection and Preparation

Successful AI-driven verification demands robust infrastructure capable of processing and storing vast quantities of verification data. Industry implementations typically require processing power ranging from 15-20 TFLOPS for real-time analysis of simulation outputs, with storage requirements growing at 2-4TB per month for active SoC verification projects [7]. Effective data pipelines must handle multiple data types simultaneously, including code coverage metrics, functional coverage points, simulation logs, and waveform data. The transition from ad-hoc data collection to structured AI-ready repositories requires defining standardized schemas and metadata tagging systems, with implementation timelines averaging 90-120 days for verification teams adapting existing infrastructures. Proper data labeling represents a crucial challenge, with studies showing that at least 2,500 labeled bug examples across 8-10 categories are needed to train initial classification models that achieve 80% accuracy on new examples [7].

## 4.2. ML Model Selection and Training

Different verification tasks demand specialized machine-learning approaches to achieve optimal results. For defect prediction applications, supervised learning models trained on historical bug data demonstrate the strongest performance, with recent implementations achieving 67-74% accuracy in identifying high-risk design elements [8]. These models typically require 5-7 weeks of training time on datasets containing thousands of historical test cases to reach stable performance levels. Reinforcement learning frameworks show particular promise for test generation, with implementations demonstrating a 32% improvement in coverage growth rate compared to traditional constrained-random approaches [8]. The training process typically involves 1,000-2,000 simulation iterations before the models demonstrate consistent performance advantages. For anomaly detection in simulation results, unsupervised learning techniques have proven effective at identifying outlier behaviors with minimal false positives, achieving precision rates of 83% after training on approximately 5,000 baseline simulation runs [8].

### 4.3. Integration with Verification Flows

Successfully integrating AI capabilities into existing verification flows requires careful attention to workflow alignment and user experience considerations. Case studies of successful implementations show that verification engineers typically require 4-6 weeks to adapt their workflows to effectively leverage AI-based tools, with productivity temporarily decreasing by 10-15% during the transition period [7]. Architectural approaches that loosely couple AI systems with existing verification infrastructure through standardized APIs minimize disruption and allow incremental adoption. Data synchronization represents a significant challenge, with real-time prediction systems requiring simulation data updates at intervals not exceeding 12-24 hours to maintain model relevance [7]. This requirement drives the growing adoption of continuous integration approaches that automatically trigger model retraining when significant design or testbench changes occur.

Human oversight remains essential for critical verification decisions, with hybrid approaches demonstrating the strongest practical results. Advanced implementations employ confidence scoring mechanisms that identify low-certainty predictions (typically 15-18% of cases) for human review [8]. This approach preserves efficiency gains while maintaining necessary quality controls. Transparency in AI decision-making significantly impacts adoption rates, with studies showing 2.4x higher utilization for tools that provide clear explanations for their recommendations. The development of specialized visualization techniques that present prediction confidence and influential features alongside traditional verification views has proven particularly effective, with users reporting 68% higher trust in explainable systems [8]. This human-centric approach requires investment in user interface design but yields significantly higher successful deployment rates compared to black-box ML systems.

**Table 1** Performance and Adoption Metrics for AI in Verification [7,8]

| Metric                                           | Value  |

|--------------------------------------------------|--------|

| Initial model accuracy                           | 80%    |

| Supervised learning accuracy range               | 67-74% |

| Coverage improvement with reinforcement learning | 32%    |

| Anomaly detection precision                      | 83%    |

| Temporary productivity decrease during adoption  | 10-15% |

# 5. Real-World Impact and Case Studies

# 5.1. Quantifiable Benefits

The implementation of AI-driven verification methodologies has delivered measurable improvements across verification metrics that translate directly to business impact. Comparative studies of projects utilizing machine learning for functional verification demonstrate a 31.4% reduction in overall verification time, with coverage closure activities showing the most significant acceleration [9]. This efficiency translates to tangible project timeline compression, with data indicating a 22-36-day reduction in verification schedules for complex SoC designs. Simulation efficiency metrics reveal that ML-optimized test suites achieve equivalent functional coverage with approximately 35%

fewer simulation cycles, significantly reducing compute infrastructure requirements. These efficiency improvements scale with design complexity, with a strong correlation coefficient of 0.78 between design size and ML-derived efficiency gains [9].

## 5.2. Case Study: AI Acceleration in Processor Verification

A detailed processor verification case study demonstrates the transformative impact of AI-driven methodologies on real-world designs. In the verification of a multi-core processor with 8 processing elements, the implementation of a reinforcement learning approach for test scenario generation resulted in the discovery of 124 previously undetected design issues, of which 27 were classified as critical functional bugs that would have impacted system operation [10]. The efficiency improvements were equally significant, with functional coverage metrics showing a 41.7% reduction in time required to achieve coverage targets compared to reference designs verified using traditional methodologies. Coverage growth analysis revealed particularly strong performance in the final verification stages, with the last 10% of coverage points reaching 2.8× faster using ML-directed test generation compared to constrained-random approaches [10].

Resource allocation metrics from the case study showed a 43% reduction in engineer time spent on manual test creation and a 37% decrease in debugging time due to more precise identification of failure root causes. This resource reallocation enabled increased focus on architectural optimization, with the team reporting a 24% increase in time devoted to performance analysis and enhancement activities [10]. The overall project timeline impact was substantial, with a 7.3-week reduction in the complete verification cycle leading to earlier market availability. The quality metrics showed corresponding improvements, with post-silicon validation reporting a 52% reduction in functional issues escaping pre-silicon verification compared to previous comparable projects verified using conventional methodologies.

# 5.3. Challenges and Limitations

Despite demonstrated benefits, organizations implementing AI-driven verification face significant adoption challenges that must be addressed. Initial implementation costs remain substantial, with research indicating average setup investments of approximately €250,000 for computing infrastructure and software licenses, plus 4-6 person-months of engineering effort to develop initial models and integration frameworks [9]. Data requirements present additional barriers, with model accuracy analysis showing that verification ML systems require training datasets from at least 2-3 previous projects of comparable complexity to achieve predictive accuracy above 75%. Organizations without this historical data face a significant "cold start" problem limiting initial effectiveness.

Integration complexity presents ongoing challenges, with survey data indicating that verification teams spend an average of 3.6 months adapting existing verification environments to support ML-guided approaches [9]. This integration period introduces temporary productivity decreases of 12-18% before systems reach operational effectiveness. User adoption represents perhaps the most persistent barrier, with studies showing that verification engineers initially trust ML-generated test scenarios 42% less than manually created equivalents. This trust gap narrows with experience, decreasing to 8-12% after approximately 6 months of regular system usage [10]. Explainability features significantly impact adoption rates, with implementations providing transparent decision rationales achieving 2.3× higher utilization rates compared to black-box approaches. Training requirements for verification engineers represent the final significant challenge, with data indicating an average learning curve of 45-60 hours of formal training plus 2-3 months of practical experience before users achieve full productivity with advanced ML verification systems.

**Table 2** Efficiency Gains from AI-Driven Verification Methodologies [9, 10]

| Metric                                             | Value |

|----------------------------------------------------|-------|

| Overall verification time reduction                | 31.4% |

| Reduction in simulation cycles                     | 35%   |

| Reduction in time to achieve coverage targets      | 41.7% |

| Reduction in engineer time for test creation       | 43%   |

| Reduction in functional issues escaping to silicon | 52%   |

## 6. Conclusion

Artificial intelligence and machine learning are fundamentally transforming functional verification in chip design, addressing the widening gap between verification requirements and traditional capabilities. By intelligently automating test generation, optimizing coverage strategies, and enabling early bug detection, these technologies shorten development cycles while improving design quality. The future points toward an increasingly autonomous verification flow where AI agents continuously learn from global verification data, predict potential issues before they manifest, and automatically generate tests for emerging corner cases. This evolution enables verification engineers to focus on architectural innovations and complex debug scenarios rather than routine test creation. Organizations that successfully integrate AI-driven verification into their workflows gain a significant competitive advantage through faster time-to-market, reduced development costs, and, ultimately, more reliable chip designs.

#### References

- [1] Katherine Derbyshire, "New Tradeoffs In Leading-Edge Chip Design," Semiconductor Engineering, 2024. [Online]. Available: https://semiengineering.com/tradeoffs-in-leading-edge-chip-design/

- [2] Siemens Digital Industries Software "2022 Wilson Research Group FPGA functional verification trends," 2022. [Online]. Available: https://www.innofour.com/static/default/files/documents/pdf/fpga-trend-report\_2022-wilson-research-verification-study\_hfoster.pdf

- [3] Ali Hmedat, "Machine Learning Application in the Verification of SoC Designs," LinkedIn, 2024. [Online]. Available: https://www.linkedin.com/pulse/machine-learning-application-verification-soc-designs-ali-hmedat-uormf/

- [4] Niranjana Gurushankar, "Trends in Semiconductor Design Verification for AI and Machine Learning Applications," International Journal For Multidisciplinary Research 4(6), 2022. [Online]. Available: https://www.researchgate.net/publication/388769013\_Trends\_in\_Semiconductor\_Design\_Verification\_for\_AI\_ and\_Machine\_Learning\_Applications

- [5] Mahmoud Elbana, "Functional Verification using Machine Learning Techniques," Thesis for: Bachelor of Science in Electronics EngineeringAdvisor: Amr Talaat, 2024. [Online]. Available: https://www.researchgate.net/publication/377919989\_Functional\_Verification\_using\_Machine\_Learning\_Techniques

- [6] Yuvaraj J Patil, "Artificial Intelligence in Functional Verification: Transforming Safety-Critical Semiconductor Design Methodologies," International Journal Of Information Technology And Management Information Systems 16(2):900-921, 2025. [Online]. Available: https://www.researchgate.net/publication/389787548\_ARTIFICIAL\_INTELLIGENCE\_IN\_FUNCTIONAL\_VERIFI CATION\_TRANSFORMING\_SAFETY-CRITICAL\_SEMICONDUCTOR\_DESIGN\_METHODOLOGIES

- [7] FP Data Solutions Team, "AI infrastructure: a comprehensive guide to building your AI stack," Future Processing, 2024. [Online]. Available: https://www.future-processing.com/blog/ai-infrastructure/

- [8] Dan Yu et al., "A Survey of Machine Learning Applications in Functional Verification." [Online]. Available: https://dvcon-proceedings.org/wp-content/uploads/1135-A-Survey-of-Machine-Learning-Applications-in-Functional-Verification.pdf

- [9] Diana Dranga and Catalin Dumitrescu, "Artificial Intelligence Application in the Field of Functional Verification," Electronics 2024, 13(12), 2024. [Online]. Available: https://www.mdpi.com/2079-9292/13/12/2361

- [10] Mohamed Ayoub Neggaz, "Hardware Accelerators for Machine Learning Applications. Case Study: Autonomous Vehicles," HAL Archives, TEL-03177513, 2021. [Online]. Available: https://theses.hal.science/tel-03177513v1/file/NEGGAZ\_Mohamed\_Ayoub2.pdf